3D VLSI Non-Slicing Floor Planning using Modified Corner List Representation Article Swipe

YOU?

·

· 2015

· Open Access

·

· DOI: https://doi.org/10.17485/ijst/2015/v8i35/81204

YOU?

·

· 2015

· Open Access

·

· DOI: https://doi.org/10.17485/ijst/2015/v8i35/81204

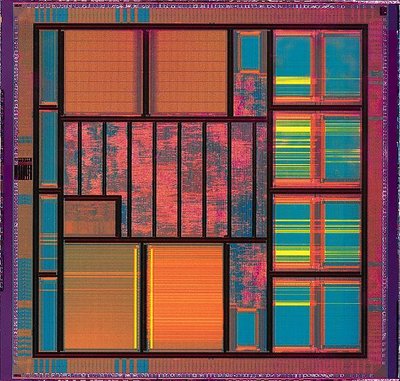

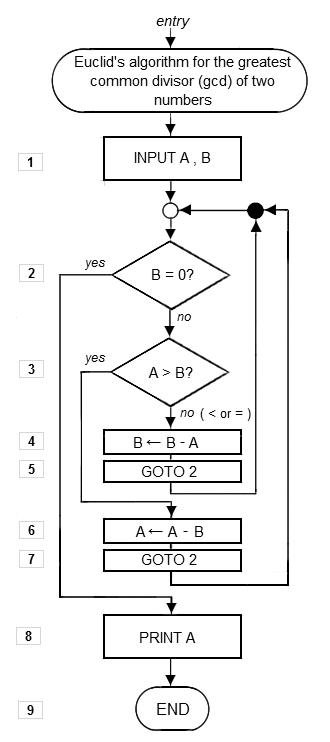

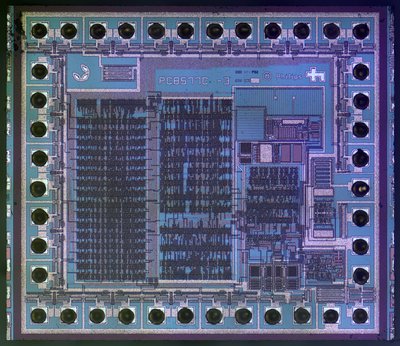

Background: Floorplanning is important step in physical design automation of VLSI circuits, because it gives an early feedback on the architectural design. It is the process of finding the position of the module such that no two modules overlap with each other. Methods: In order to have an efficient floorplan, the total area occupied by the modules should be minimum. So, non-slicing floorplan is used to find an optimal floorplan layout. To represent non-slicing floorplan, a number of representations are proposed. Findings: To encompass billions of transistors in an Integrated Circuit (IC), 3Dimensional (3D) IC is preferred instead of 2D. In this paper, a novel 3Dimensional (3D) non-slicing floorplanning representation called Modified Corner List (MCL) algorithm is proposed and properties of MCL algorithm is derived. The proposed algorithm is illustrated using Microelectronics Centre of North Carolina (MCNC) benchmark circuits and simulation results shows that it is very effective for 3D floorplan representation. Improvements: The proposed algorithm works well for small number of modules. As the number of module increases, computational time taken by the algorithm also increases. The above problem can be solved by applying heuristic algorithm in association with MCL strategy to find near optimal placement in reduced run time.Keywords: MCNC Benchmark Circuits, Modified Corner List, 3D Non-Slicing Floorplan, VLSI

Related Topics

- Type

- article

- Language

- en

- Landing Page

- https://doi.org/10.17485/ijst/2015/v8i35/81204

- http://www.indjst.org/index.php/indjst/article/download/81204/65468

- OA Status

- diamond

- Cited By

- 3

- References

- 15

- Related Works

- 10

- OpenAlex ID

- https://openalex.org/W2198836535

Raw OpenAlex JSON

- OpenAlex ID

-

https://openalex.org/W2198836535Canonical identifier for this work in OpenAlex

- DOI

-

https://doi.org/10.17485/ijst/2015/v8i35/81204Digital Object Identifier

- Title

-

3D VLSI Non-Slicing Floor Planning using Modified Corner List RepresentationWork title

- Type

-

articleOpenAlex work type

- Language

-

enPrimary language

- Publication year

-

2015Year of publication

- Publication date

-

2015-12-28Full publication date if available

- Authors

-

P. Sivaranjani, A. Senthil KumarList of authors in order

- Landing page

-

https://doi.org/10.17485/ijst/2015/v8i35/81204Publisher landing page

- PDF URL

-

https://www.indjst.org/index.php/indjst/article/download/81204/65468Direct link to full text PDF

- Open access

-

YesWhether a free full text is available

- OA status

-

diamondOpen access status per OpenAlex

- OA URL

-

https://www.indjst.org/index.php/indjst/article/download/81204/65468Direct OA link when available

- Concepts

-

Floorplan, Very-large-scale integration, Computer science, Slicing, Benchmark (surveying), Algorithm, Physical design, Representation (politics), Integrated circuit layout, Heuristic, Integrated circuit, Routing (electronic design automation), Computer engineering, Parallel computing, Circuit design, Embedded system, Artificial intelligence, Politics, Geodesy, Geography, Operating system, Law, World Wide Web, Political scienceTop concepts (fields/topics) attached by OpenAlex

- Cited by

-

3Total citation count in OpenAlex

- Citations by year (recent)

-

2021: 1, 2016: 2Per-year citation counts (last 5 years)

- References (count)

-

15Number of works referenced by this work

- Related works (count)

-

10Other works algorithmically related by OpenAlex

Full payload

| id | https://openalex.org/W2198836535 |

|---|---|

| doi | https://doi.org/10.17485/ijst/2015/v8i35/81204 |

| ids.doi | https://doi.org/10.17485/ijst/2015/v8i35/81204 |

| ids.mag | 2198836535 |

| ids.openalex | https://openalex.org/W2198836535 |

| fwci | 0.33415777 |

| type | article |

| title | 3D VLSI Non-Slicing Floor Planning using Modified Corner List Representation |

| biblio.issue | 35 |

| biblio.volume | 8 |

| biblio.last_page | |

| biblio.first_page | |

| topics[0].id | https://openalex.org/T11522 |

| topics[0].field.id | https://openalex.org/fields/22 |

| topics[0].field.display_name | Engineering |

| topics[0].score | 0.9998999834060669 |

| topics[0].domain.id | https://openalex.org/domains/3 |

| topics[0].domain.display_name | Physical Sciences |

| topics[0].subfield.id | https://openalex.org/subfields/2208 |

| topics[0].subfield.display_name | Electrical and Electronic Engineering |

| topics[0].display_name | VLSI and FPGA Design Techniques |

| topics[1].id | https://openalex.org/T11527 |

| topics[1].field.id | https://openalex.org/fields/22 |

| topics[1].field.display_name | Engineering |

| topics[1].score | 0.9995999932289124 |

| topics[1].domain.id | https://openalex.org/domains/3 |

| topics[1].domain.display_name | Physical Sciences |

| topics[1].subfield.id | https://openalex.org/subfields/2208 |

| topics[1].subfield.display_name | Electrical and Electronic Engineering |

| topics[1].display_name | 3D IC and TSV technologies |

| topics[2].id | https://openalex.org/T11338 |

| topics[2].field.id | https://openalex.org/fields/22 |

| topics[2].field.display_name | Engineering |

| topics[2].score | 0.9980000257492065 |

| topics[2].domain.id | https://openalex.org/domains/3 |

| topics[2].domain.display_name | Physical Sciences |

| topics[2].subfield.id | https://openalex.org/subfields/2208 |

| topics[2].subfield.display_name | Electrical and Electronic Engineering |

| topics[2].display_name | Advancements in Photolithography Techniques |

| is_xpac | False |

| apc_list | |

| apc_paid | |

| concepts[0].id | https://openalex.org/C130145326 |

| concepts[0].level | 2 |

| concepts[0].score | 0.9789872169494629 |

| concepts[0].wikidata | https://www.wikidata.org/wiki/Q1553985 |

| concepts[0].display_name | Floorplan |

| concepts[1].id | https://openalex.org/C14580979 |

| concepts[1].level | 2 |

| concepts[1].score | 0.7704654932022095 |

| concepts[1].wikidata | https://www.wikidata.org/wiki/Q876049 |

| concepts[1].display_name | Very-large-scale integration |

| concepts[2].id | https://openalex.org/C41008148 |

| concepts[2].level | 0 |

| concepts[2].score | 0.7347424626350403 |

| concepts[2].wikidata | https://www.wikidata.org/wiki/Q21198 |

| concepts[2].display_name | Computer science |

| concepts[3].id | https://openalex.org/C2776190703 |

| concepts[3].level | 2 |

| concepts[3].score | 0.700752854347229 |

| concepts[3].wikidata | https://www.wikidata.org/wiki/Q488148 |

| concepts[3].display_name | Slicing |

| concepts[4].id | https://openalex.org/C185798385 |

| concepts[4].level | 2 |

| concepts[4].score | 0.6772902011871338 |

| concepts[4].wikidata | https://www.wikidata.org/wiki/Q1161707 |

| concepts[4].display_name | Benchmark (surveying) |

| concepts[5].id | https://openalex.org/C11413529 |

| concepts[5].level | 1 |

| concepts[5].score | 0.542726457118988 |

| concepts[5].wikidata | https://www.wikidata.org/wiki/Q8366 |

| concepts[5].display_name | Algorithm |

| concepts[6].id | https://openalex.org/C188817802 |

| concepts[6].level | 3 |

| concepts[6].score | 0.5140272378921509 |

| concepts[6].wikidata | https://www.wikidata.org/wiki/Q13426855 |

| concepts[6].display_name | Physical design |

| concepts[7].id | https://openalex.org/C2776359362 |

| concepts[7].level | 3 |

| concepts[7].score | 0.5088577270507812 |

| concepts[7].wikidata | https://www.wikidata.org/wiki/Q2145286 |

| concepts[7].display_name | Representation (politics) |

| concepts[8].id | https://openalex.org/C2765594 |

| concepts[8].level | 3 |

| concepts[8].score | 0.47310447692871094 |

| concepts[8].wikidata | https://www.wikidata.org/wiki/Q2624187 |

| concepts[8].display_name | Integrated circuit layout |

| concepts[9].id | https://openalex.org/C173801870 |

| concepts[9].level | 2 |

| concepts[9].score | 0.45856061577796936 |

| concepts[9].wikidata | https://www.wikidata.org/wiki/Q201413 |

| concepts[9].display_name | Heuristic |

| concepts[10].id | https://openalex.org/C530198007 |

| concepts[10].level | 2 |

| concepts[10].score | 0.43196696043014526 |

| concepts[10].wikidata | https://www.wikidata.org/wiki/Q80831 |

| concepts[10].display_name | Integrated circuit |

| concepts[11].id | https://openalex.org/C74172769 |

| concepts[11].level | 2 |

| concepts[11].score | 0.41577377915382385 |

| concepts[11].wikidata | https://www.wikidata.org/wiki/Q1446839 |

| concepts[11].display_name | Routing (electronic design automation) |

| concepts[12].id | https://openalex.org/C113775141 |

| concepts[12].level | 1 |

| concepts[12].score | 0.3798740804195404 |

| concepts[12].wikidata | https://www.wikidata.org/wiki/Q428691 |

| concepts[12].display_name | Computer engineering |

| concepts[13].id | https://openalex.org/C173608175 |

| concepts[13].level | 1 |

| concepts[13].score | 0.34480446577072144 |

| concepts[13].wikidata | https://www.wikidata.org/wiki/Q232661 |

| concepts[13].display_name | Parallel computing |

| concepts[14].id | https://openalex.org/C190560348 |

| concepts[14].level | 2 |

| concepts[14].score | 0.2788545787334442 |

| concepts[14].wikidata | https://www.wikidata.org/wiki/Q3245116 |

| concepts[14].display_name | Circuit design |

| concepts[15].id | https://openalex.org/C149635348 |

| concepts[15].level | 1 |

| concepts[15].score | 0.16946375370025635 |

| concepts[15].wikidata | https://www.wikidata.org/wiki/Q193040 |

| concepts[15].display_name | Embedded system |

| concepts[16].id | https://openalex.org/C154945302 |

| concepts[16].level | 1 |

| concepts[16].score | 0.11902579665184021 |

| concepts[16].wikidata | https://www.wikidata.org/wiki/Q11660 |

| concepts[16].display_name | Artificial intelligence |

| concepts[17].id | https://openalex.org/C94625758 |

| concepts[17].level | 2 |

| concepts[17].score | 0.0 |

| concepts[17].wikidata | https://www.wikidata.org/wiki/Q7163 |

| concepts[17].display_name | Politics |

| concepts[18].id | https://openalex.org/C13280743 |

| concepts[18].level | 1 |

| concepts[18].score | 0.0 |

| concepts[18].wikidata | https://www.wikidata.org/wiki/Q131089 |

| concepts[18].display_name | Geodesy |

| concepts[19].id | https://openalex.org/C205649164 |

| concepts[19].level | 0 |

| concepts[19].score | 0.0 |

| concepts[19].wikidata | https://www.wikidata.org/wiki/Q1071 |

| concepts[19].display_name | Geography |

| concepts[20].id | https://openalex.org/C111919701 |

| concepts[20].level | 1 |

| concepts[20].score | 0.0 |

| concepts[20].wikidata | https://www.wikidata.org/wiki/Q9135 |

| concepts[20].display_name | Operating system |

| concepts[21].id | https://openalex.org/C199539241 |

| concepts[21].level | 1 |

| concepts[21].score | 0.0 |

| concepts[21].wikidata | https://www.wikidata.org/wiki/Q7748 |

| concepts[21].display_name | Law |

| concepts[22].id | https://openalex.org/C136764020 |

| concepts[22].level | 1 |

| concepts[22].score | 0.0 |

| concepts[22].wikidata | https://www.wikidata.org/wiki/Q466 |

| concepts[22].display_name | World Wide Web |

| concepts[23].id | https://openalex.org/C17744445 |

| concepts[23].level | 0 |

| concepts[23].score | 0.0 |

| concepts[23].wikidata | https://www.wikidata.org/wiki/Q36442 |

| concepts[23].display_name | Political science |

| keywords[0].id | https://openalex.org/keywords/floorplan |

| keywords[0].score | 0.9789872169494629 |

| keywords[0].display_name | Floorplan |

| keywords[1].id | https://openalex.org/keywords/very-large-scale-integration |

| keywords[1].score | 0.7704654932022095 |

| keywords[1].display_name | Very-large-scale integration |

| keywords[2].id | https://openalex.org/keywords/computer-science |

| keywords[2].score | 0.7347424626350403 |

| keywords[2].display_name | Computer science |

| keywords[3].id | https://openalex.org/keywords/slicing |

| keywords[3].score | 0.700752854347229 |

| keywords[3].display_name | Slicing |

| keywords[4].id | https://openalex.org/keywords/benchmark |

| keywords[4].score | 0.6772902011871338 |

| keywords[4].display_name | Benchmark (surveying) |

| keywords[5].id | https://openalex.org/keywords/algorithm |

| keywords[5].score | 0.542726457118988 |

| keywords[5].display_name | Algorithm |

| keywords[6].id | https://openalex.org/keywords/physical-design |

| keywords[6].score | 0.5140272378921509 |

| keywords[6].display_name | Physical design |

| keywords[7].id | https://openalex.org/keywords/representation |

| keywords[7].score | 0.5088577270507812 |

| keywords[7].display_name | Representation (politics) |

| keywords[8].id | https://openalex.org/keywords/integrated-circuit-layout |

| keywords[8].score | 0.47310447692871094 |

| keywords[8].display_name | Integrated circuit layout |

| keywords[9].id | https://openalex.org/keywords/heuristic |

| keywords[9].score | 0.45856061577796936 |

| keywords[9].display_name | Heuristic |

| keywords[10].id | https://openalex.org/keywords/integrated-circuit |

| keywords[10].score | 0.43196696043014526 |

| keywords[10].display_name | Integrated circuit |

| keywords[11].id | https://openalex.org/keywords/routing |

| keywords[11].score | 0.41577377915382385 |

| keywords[11].display_name | Routing (electronic design automation) |

| keywords[12].id | https://openalex.org/keywords/computer-engineering |

| keywords[12].score | 0.3798740804195404 |

| keywords[12].display_name | Computer engineering |

| keywords[13].id | https://openalex.org/keywords/parallel-computing |

| keywords[13].score | 0.34480446577072144 |

| keywords[13].display_name | Parallel computing |

| keywords[14].id | https://openalex.org/keywords/circuit-design |

| keywords[14].score | 0.2788545787334442 |

| keywords[14].display_name | Circuit design |

| keywords[15].id | https://openalex.org/keywords/embedded-system |

| keywords[15].score | 0.16946375370025635 |

| keywords[15].display_name | Embedded system |

| keywords[16].id | https://openalex.org/keywords/artificial-intelligence |

| keywords[16].score | 0.11902579665184021 |

| keywords[16].display_name | Artificial intelligence |

| language | en |

| locations[0].id | doi:10.17485/ijst/2015/v8i35/81204 |

| locations[0].is_oa | True |

| locations[0].source.id | https://openalex.org/S2764746358 |

| locations[0].source.issn | 0974-5645, 0974-6846 |

| locations[0].source.type | journal |

| locations[0].source.is_oa | True |

| locations[0].source.issn_l | 0974-5645 |

| locations[0].source.is_core | True |

| locations[0].source.is_in_doaj | False |

| locations[0].source.display_name | Indian Journal of Science and Technology |

| locations[0].source.host_organization | https://openalex.org/P4322615647 |

| locations[0].source.host_organization_name | Indian Society for Education and Environment |

| locations[0].source.host_organization_lineage | https://openalex.org/P4322615647 |

| locations[0].source.host_organization_lineage_names | Indian Society for Education and Environment |

| locations[0].license | cc-by |

| locations[0].pdf_url | http://www.indjst.org/index.php/indjst/article/download/81204/65468 |

| locations[0].version | publishedVersion |

| locations[0].raw_type | journal-article |

| locations[0].license_id | https://openalex.org/licenses/cc-by |

| locations[0].is_accepted | True |

| locations[0].is_published | True |

| locations[0].raw_source_name | Indian Journal of Science and Technology |

| locations[0].landing_page_url | https://doi.org/10.17485/ijst/2015/v8i35/81204 |

| indexed_in | crossref |

| authorships[0].author.id | https://openalex.org/A5039582689 |

| authorships[0].author.orcid | |

| authorships[0].author.display_name | P. Sivaranjani |

| authorships[0].affiliations[0].raw_affiliation_string | Department of Electronics and Communication Engineering, Kongu Engineering College, Perundurai – 638052,#R##N#Tamil Nadu |

| authorships[0].author_position | first |

| authorships[0].raw_author_name | P. Sivaranjani |

| authorships[0].is_corresponding | False |

| authorships[0].raw_affiliation_strings | Department of Electronics and Communication Engineering, Kongu Engineering College, Perundurai – 638052,#R##N#Tamil Nadu |

| authorships[1].author.id | https://openalex.org/A5074285622 |

| authorships[1].author.orcid | https://orcid.org/0000-0002-8468-9348 |

| authorships[1].author.display_name | A. Senthil Kumar |

| authorships[1].affiliations[0].raw_affiliation_string | Department of Electrical and Electronics Engineering, Dr. Mahalingam College of Engineering and Technology, Pollachi - 642003, Tamil Nadu |

| authorships[1].author_position | last |

| authorships[1].raw_author_name | A. Senthil Kumar |

| authorships[1].is_corresponding | False |

| authorships[1].raw_affiliation_strings | Department of Electrical and Electronics Engineering, Dr. Mahalingam College of Engineering and Technology, Pollachi - 642003, Tamil Nadu |

| has_content.pdf | True |

| has_content.grobid_xml | True |

| is_paratext | False |

| open_access.is_oa | True |

| open_access.oa_url | http://www.indjst.org/index.php/indjst/article/download/81204/65468 |

| open_access.oa_status | diamond |

| open_access.any_repository_has_fulltext | False |

| created_date | 2025-10-10T00:00:00 |

| display_name | 3D VLSI Non-Slicing Floor Planning using Modified Corner List Representation |

| has_fulltext | False |

| is_retracted | False |

| updated_date | 2025-11-06T03:46:38.306776 |

| primary_topic.id | https://openalex.org/T11522 |

| primary_topic.field.id | https://openalex.org/fields/22 |

| primary_topic.field.display_name | Engineering |

| primary_topic.score | 0.9998999834060669 |

| primary_topic.domain.id | https://openalex.org/domains/3 |

| primary_topic.domain.display_name | Physical Sciences |

| primary_topic.subfield.id | https://openalex.org/subfields/2208 |

| primary_topic.subfield.display_name | Electrical and Electronic Engineering |

| primary_topic.display_name | VLSI and FPGA Design Techniques |

| related_works | https://openalex.org/W2157271968, https://openalex.org/W2158448234, https://openalex.org/W1523582517, https://openalex.org/W1984375234, https://openalex.org/W2115502122, https://openalex.org/W2005457717, https://openalex.org/W2138401961, https://openalex.org/W2353155791, https://openalex.org/W2109972882, https://openalex.org/W2036121598 |

| cited_by_count | 3 |

| counts_by_year[0].year | 2021 |

| counts_by_year[0].cited_by_count | 1 |

| counts_by_year[1].year | 2016 |

| counts_by_year[1].cited_by_count | 2 |

| locations_count | 1 |

| best_oa_location.id | doi:10.17485/ijst/2015/v8i35/81204 |

| best_oa_location.is_oa | True |

| best_oa_location.source.id | https://openalex.org/S2764746358 |

| best_oa_location.source.issn | 0974-5645, 0974-6846 |

| best_oa_location.source.type | journal |

| best_oa_location.source.is_oa | True |

| best_oa_location.source.issn_l | 0974-5645 |

| best_oa_location.source.is_core | True |

| best_oa_location.source.is_in_doaj | False |

| best_oa_location.source.display_name | Indian Journal of Science and Technology |

| best_oa_location.source.host_organization | https://openalex.org/P4322615647 |

| best_oa_location.source.host_organization_name | Indian Society for Education and Environment |

| best_oa_location.source.host_organization_lineage | https://openalex.org/P4322615647 |

| best_oa_location.source.host_organization_lineage_names | Indian Society for Education and Environment |

| best_oa_location.license | cc-by |

| best_oa_location.pdf_url | http://www.indjst.org/index.php/indjst/article/download/81204/65468 |

| best_oa_location.version | publishedVersion |

| best_oa_location.raw_type | journal-article |

| best_oa_location.license_id | https://openalex.org/licenses/cc-by |

| best_oa_location.is_accepted | True |

| best_oa_location.is_published | True |

| best_oa_location.raw_source_name | Indian Journal of Science and Technology |

| best_oa_location.landing_page_url | https://doi.org/10.17485/ijst/2015/v8i35/81204 |

| primary_location.id | doi:10.17485/ijst/2015/v8i35/81204 |

| primary_location.is_oa | True |

| primary_location.source.id | https://openalex.org/S2764746358 |

| primary_location.source.issn | 0974-5645, 0974-6846 |

| primary_location.source.type | journal |

| primary_location.source.is_oa | True |

| primary_location.source.issn_l | 0974-5645 |

| primary_location.source.is_core | True |

| primary_location.source.is_in_doaj | False |

| primary_location.source.display_name | Indian Journal of Science and Technology |

| primary_location.source.host_organization | https://openalex.org/P4322615647 |

| primary_location.source.host_organization_name | Indian Society for Education and Environment |

| primary_location.source.host_organization_lineage | https://openalex.org/P4322615647 |

| primary_location.source.host_organization_lineage_names | Indian Society for Education and Environment |

| primary_location.license | cc-by |

| primary_location.pdf_url | http://www.indjst.org/index.php/indjst/article/download/81204/65468 |

| primary_location.version | publishedVersion |

| primary_location.raw_type | journal-article |

| primary_location.license_id | https://openalex.org/licenses/cc-by |

| primary_location.is_accepted | True |

| primary_location.is_published | True |

| primary_location.raw_source_name | Indian Journal of Science and Technology |

| primary_location.landing_page_url | https://doi.org/10.17485/ijst/2015/v8i35/81204 |

| publication_date | 2015-12-28 |

| publication_year | 2015 |

| referenced_works | https://openalex.org/W1541633348, https://openalex.org/W2052274298, https://openalex.org/W2152472834, https://openalex.org/W1544642978, https://openalex.org/W2138789181, https://openalex.org/W2153770483, https://openalex.org/W2183935829, https://openalex.org/W2120914420, https://openalex.org/W2127012874, https://openalex.org/W2110514755, https://openalex.org/W2154462472, https://openalex.org/W1969484022, https://openalex.org/W1902269752, https://openalex.org/W631225564, https://openalex.org/W2141235761 |

| referenced_works_count | 15 |

| abstract_inverted_index.a | 75, 103 |

| abstract_inverted_index.3D | 149, 207 |

| abstract_inverted_index.As | 163 |

| abstract_inverted_index.IC | 94 |

| abstract_inverted_index.In | 43, 100 |

| abstract_inverted_index.It | 22 |

| abstract_inverted_index.To | 71, 82 |

| abstract_inverted_index.an | 15, 47, 67, 88 |

| abstract_inverted_index.be | 58, 181 |

| abstract_inverted_index.by | 54, 172, 183 |

| abstract_inverted_index.in | 5, 87, 187, 197 |

| abstract_inverted_index.is | 2, 23, 63, 95, 116, 123, 128, 145 |

| abstract_inverted_index.it | 13, 144 |

| abstract_inverted_index.no | 35 |

| abstract_inverted_index.of | 9, 26, 30, 77, 85, 98, 120, 133, 161, 166 |

| abstract_inverted_index.on | 18 |

| abstract_inverted_index.to | 45, 65, 192 |

| abstract_inverted_index.2D. | 99 |

| abstract_inverted_index.MCL | 121, 190 |

| abstract_inverted_index.So, | 60 |

| abstract_inverted_index.The | 125, 153, 177 |

| abstract_inverted_index.and | 118, 139 |

| abstract_inverted_index.are | 79 |

| abstract_inverted_index.can | 180 |

| abstract_inverted_index.for | 148, 158 |

| abstract_inverted_index.run | 199 |

| abstract_inverted_index.the | 19, 24, 28, 31, 50, 55, 164, 173 |

| abstract_inverted_index.two | 36 |

| abstract_inverted_index.(3D) | 93, 106 |

| abstract_inverted_index.List | 113 |

| abstract_inverted_index.MCNC | 201 |

| abstract_inverted_index.VLSI | 10, 210 |

| abstract_inverted_index.also | 175 |

| abstract_inverted_index.area | 52 |

| abstract_inverted_index.each | 40 |

| abstract_inverted_index.find | 66, 193 |

| abstract_inverted_index.have | 46 |

| abstract_inverted_index.near | 194 |

| abstract_inverted_index.step | 4 |

| abstract_inverted_index.such | 33 |

| abstract_inverted_index.that | 34, 143 |

| abstract_inverted_index.this | 101 |

| abstract_inverted_index.time | 170 |

| abstract_inverted_index.used | 64 |

| abstract_inverted_index.very | 146 |

| abstract_inverted_index.well | 157 |

| abstract_inverted_index.with | 39, 189 |

| abstract_inverted_index.(IC), | 91 |

| abstract_inverted_index.(MCL) | 114 |

| abstract_inverted_index.List, | 206 |

| abstract_inverted_index.North | 134 |

| abstract_inverted_index.above | 178 |

| abstract_inverted_index.early | 16 |

| abstract_inverted_index.gives | 14 |

| abstract_inverted_index.novel | 104 |

| abstract_inverted_index.order | 44 |

| abstract_inverted_index.shows | 142 |

| abstract_inverted_index.small | 159 |

| abstract_inverted_index.taken | 171 |

| abstract_inverted_index.total | 51 |

| abstract_inverted_index.using | 130 |

| abstract_inverted_index.works | 156 |

| abstract_inverted_index.(MCNC) | 136 |

| abstract_inverted_index.Centre | 132 |

| abstract_inverted_index.Corner | 112, 205 |

| abstract_inverted_index.called | 110 |

| abstract_inverted_index.design | 7 |

| abstract_inverted_index.module | 32, 167 |

| abstract_inverted_index.number | 76, 160, 165 |

| abstract_inverted_index.other. | 41 |

| abstract_inverted_index.paper, | 102 |

| abstract_inverted_index.should | 57 |

| abstract_inverted_index.solved | 182 |

| abstract_inverted_index.Circuit | 90 |

| abstract_inverted_index.because | 12 |

| abstract_inverted_index.design. | 21 |

| abstract_inverted_index.finding | 27 |

| abstract_inverted_index.instead | 97 |

| abstract_inverted_index.layout. | 70 |

| abstract_inverted_index.modules | 37, 56 |

| abstract_inverted_index.optimal | 68, 195 |

| abstract_inverted_index.overlap | 38 |

| abstract_inverted_index.problem | 179 |

| abstract_inverted_index.process | 25 |

| abstract_inverted_index.reduced | 198 |

| abstract_inverted_index.results | 141 |

| abstract_inverted_index.Carolina | 135 |

| abstract_inverted_index.Methods: | 42 |

| abstract_inverted_index.Modified | 111, 204 |

| abstract_inverted_index.applying | 184 |

| abstract_inverted_index.billions | 84 |

| abstract_inverted_index.circuits | 138 |

| abstract_inverted_index.derived. | 124 |

| abstract_inverted_index.feedback | 17 |

| abstract_inverted_index.minimum. | 59 |

| abstract_inverted_index.modules. | 162 |

| abstract_inverted_index.occupied | 53 |

| abstract_inverted_index.physical | 6 |

| abstract_inverted_index.position | 29 |

| abstract_inverted_index.proposed | 117, 126, 154 |

| abstract_inverted_index.strategy | 191 |

| abstract_inverted_index.Benchmark | 202 |

| abstract_inverted_index.Circuits, | 203 |

| abstract_inverted_index.Findings: | 81 |

| abstract_inverted_index.algorithm | 115, 122, 127, 155, 174, 186 |

| abstract_inverted_index.benchmark | 137 |

| abstract_inverted_index.circuits, | 11 |

| abstract_inverted_index.effective | 147 |

| abstract_inverted_index.efficient | 48 |

| abstract_inverted_index.encompass | 83 |

| abstract_inverted_index.floorplan | 62, 69, 150 |

| abstract_inverted_index.heuristic | 185 |

| abstract_inverted_index.important | 3 |

| abstract_inverted_index.placement | 196 |

| abstract_inverted_index.preferred | 96 |

| abstract_inverted_index.proposed. | 80 |

| abstract_inverted_index.represent | 72 |

| abstract_inverted_index.Floorplan, | 209 |

| abstract_inverted_index.Integrated | 89 |

| abstract_inverted_index.automation | 8 |

| abstract_inverted_index.floorplan, | 49, 74 |

| abstract_inverted_index.increases, | 168 |

| abstract_inverted_index.increases. | 176 |

| abstract_inverted_index.properties | 119 |

| abstract_inverted_index.simulation | 140 |

| abstract_inverted_index.Background: | 0 |

| abstract_inverted_index.Non-Slicing | 208 |

| abstract_inverted_index.association | 188 |

| abstract_inverted_index.illustrated | 129 |

| abstract_inverted_index.non-slicing | 61, 73, 107 |

| abstract_inverted_index.transistors | 86 |

| abstract_inverted_index.3Dimensional | 92, 105 |

| abstract_inverted_index.Floorplanning | 1 |

| abstract_inverted_index.Improvements: | 152 |

| abstract_inverted_index.architectural | 20 |

| abstract_inverted_index.computational | 169 |

| abstract_inverted_index.floorplanning | 108 |

| abstract_inverted_index.representation | 109 |

| abstract_inverted_index.time.Keywords: | 200 |

| abstract_inverted_index.representation. | 151 |

| abstract_inverted_index.representations | 78 |

| abstract_inverted_index.Microelectronics | 131 |

| cited_by_percentile_year.max | 96 |

| cited_by_percentile_year.min | 89 |

| countries_distinct_count | 0 |

| institutions_distinct_count | 2 |

| sustainable_development_goals[0].id | https://metadata.un.org/sdg/11 |

| sustainable_development_goals[0].score | 0.800000011920929 |

| sustainable_development_goals[0].display_name | Sustainable cities and communities |

| citation_normalized_percentile.value | 0.68579687 |

| citation_normalized_percentile.is_in_top_1_percent | False |

| citation_normalized_percentile.is_in_top_10_percent | False |