A 36 MW, 13 B, 2.1 MS/S MULTI-BIT DS ADC IN 0.18 M DIGITAL CMOS PROCESS USING AN EFFICIENT TOP-DOWN DESIGN METHODOLOGY Article Swipe

Mona Safi-Harb

,

Gordon W. Roberts

·

YOU?

·

· 2021

· Open Access

·

· DOI: https://doi.org/10.36724/2664-066x-2021-7-4-7-11

YOU?

·

· 2021

· Open Access

·

· DOI: https://doi.org/10.36724/2664-066x-2021-7-4-7-11

YOU?

·

· 2021

· Open Access

·

· DOI: https://doi.org/10.36724/2664-066x-2021-7-4-7-11

YOU?

·

· 2021

· Open Access

·

· DOI: https://doi.org/10.36724/2664-066x-2021-7-4-7-11

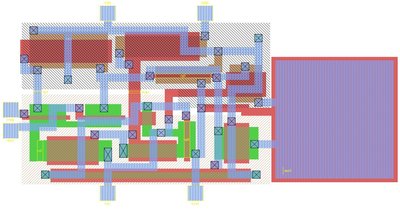

A systematic method to design a switched-capacitor (SC) multi-bit DS ADC integrated circuit is presented. The modulator consists of a fourth-order, multi-stage (2-1-1) architecture, with a 3-bit fash ADC in the last stage only. The modulator building blocks specifcations were designed using a systematic top-down methodology. Trade-offs between circuit building block specifcations, optimization time and computing resources are derived. When sampled at 50 MHz, measured performance reveals an 81.3 dB dynamic range for an output Nyquist rate of 2.1 MS/s while using a single 1.8 V supply and dissipating 36 mW of power.

Related Topics

Concepts

CMOS

Block (permutation group theory)

Capacitor

Dynamic range

Switched capacitor

Electronic engineering

Nyquist–Shannon sampling theorem

Computer science

12-bit

Decimation

Integrated circuit design

Nyquist rate

Electrical engineering

Engineering

Telecommunications

Mathematics

Sampling (signal processing)

Bandwidth (computing)

Voltage

Geometry

Detector

Metadata

- Type

- article

- Language

- en

- Landing Page

- http://doi.org/10.36724/2664-066x-2021-7-4-7-11

- https://doi.org/10.36724/2664-066x-2021-7-4-7-11

- OA Status

- diamond

- References

- 3

- Related Works

- 10

- OpenAlex ID

- https://openalex.org/W4317415683

All OpenAlex metadata

Raw OpenAlex JSON

- OpenAlex ID

-

https://openalex.org/W4317415683Canonical identifier for this work in OpenAlex

- DOI

-

https://doi.org/10.36724/2664-066x-2021-7-4-7-11Digital Object Identifier

- Title

-

A 36 MW, 13 B, 2.1 MS/S MULTI-BIT DS ADC IN 0.18 M DIGITAL CMOS PROCESS USING AN EFFICIENT TOP-DOWN DESIGN METHODOLOGYWork title

- Type

-

articleOpenAlex work type

- Language

-

enPrimary language

- Publication year

-

2021Year of publication

- Publication date

-

2021-01-01Full publication date if available

- Authors

-

Mona Safi-Harb, Gordon W. RobertsList of authors in order

- Landing page

-

https://doi.org/10.36724/2664-066x-2021-7-4-7-11Publisher landing page

- PDF URL

-

https://doi.org/10.36724/2664-066x-2021-7-4-7-11Direct link to full text PDF

- Open access

-

YesWhether a free full text is available

- OA status

-

diamondOpen access status per OpenAlex

- OA URL

-

https://doi.org/10.36724/2664-066x-2021-7-4-7-11Direct OA link when available

- Concepts

-

CMOS, Block (permutation group theory), Capacitor, Dynamic range, Switched capacitor, Electronic engineering, Nyquist–Shannon sampling theorem, Computer science, 12-bit, Decimation, Integrated circuit design, Nyquist rate, Electrical engineering, Engineering, Telecommunications, Mathematics, Sampling (signal processing), Bandwidth (computing), Voltage, Geometry, DetectorTop concepts (fields/topics) attached by OpenAlex

- Cited by

-

0Total citation count in OpenAlex

- References (count)

-

3Number of works referenced by this work

- Related works (count)

-

10Other works algorithmically related by OpenAlex

Full payload

| id | https://openalex.org/W4317415683 |

|---|---|

| doi | https://doi.org/10.36724/2664-066x-2021-7-4-7-11 |

| ids.doi | https://doi.org/10.36724/2664-066x-2021-7-4-7-11 |

| ids.openalex | https://openalex.org/W4317415683 |

| fwci | 0.0 |

| type | article |

| title | A 36 MW, 13 B, 2.1 MS/S MULTI-BIT DS ADC IN 0.18 M DIGITAL CMOS PROCESS USING AN EFFICIENT TOP-DOWN DESIGN METHODOLOGY |

| biblio.issue | 4 |

| biblio.volume | 7 |

| biblio.last_page | 11 |

| biblio.first_page | 7 |

| topics[0].id | https://openalex.org/T10323 |

| topics[0].field.id | https://openalex.org/fields/22 |

| topics[0].field.display_name | Engineering |

| topics[0].score | 1.0 |

| topics[0].domain.id | https://openalex.org/domains/3 |

| topics[0].domain.display_name | Physical Sciences |

| topics[0].subfield.id | https://openalex.org/subfields/2204 |

| topics[0].subfield.display_name | Biomedical Engineering |

| topics[0].display_name | Analog and Mixed-Signal Circuit Design |

| topics[1].id | https://openalex.org/T10558 |

| topics[1].field.id | https://openalex.org/fields/22 |

| topics[1].field.display_name | Engineering |

| topics[1].score | 0.9990000128746033 |

| topics[1].domain.id | https://openalex.org/domains/3 |

| topics[1].domain.display_name | Physical Sciences |

| topics[1].subfield.id | https://openalex.org/subfields/2208 |

| topics[1].subfield.display_name | Electrical and Electronic Engineering |

| topics[1].display_name | Advancements in Semiconductor Devices and Circuit Design |

| topics[2].id | https://openalex.org/T10187 |

| topics[2].field.id | https://openalex.org/fields/22 |

| topics[2].field.display_name | Engineering |

| topics[2].score | 0.9987999796867371 |

| topics[2].domain.id | https://openalex.org/domains/3 |

| topics[2].domain.display_name | Physical Sciences |

| topics[2].subfield.id | https://openalex.org/subfields/2208 |

| topics[2].subfield.display_name | Electrical and Electronic Engineering |

| topics[2].display_name | Radio Frequency Integrated Circuit Design |

| is_xpac | False |

| apc_list | |

| apc_paid | |

| concepts[0].id | https://openalex.org/C46362747 |

| concepts[0].level | 2 |

| concepts[0].score | 0.6665563583374023 |

| concepts[0].wikidata | https://www.wikidata.org/wiki/Q173431 |

| concepts[0].display_name | CMOS |

| concepts[1].id | https://openalex.org/C2777210771 |

| concepts[1].level | 2 |

| concepts[1].score | 0.5740953683853149 |

| concepts[1].wikidata | https://www.wikidata.org/wiki/Q4927124 |

| concepts[1].display_name | Block (permutation group theory) |

| concepts[2].id | https://openalex.org/C52192207 |

| concepts[2].level | 3 |

| concepts[2].score | 0.5188025832176208 |

| concepts[2].wikidata | https://www.wikidata.org/wiki/Q5322 |

| concepts[2].display_name | Capacitor |

| concepts[3].id | https://openalex.org/C87133666 |

| concepts[3].level | 2 |

| concepts[3].score | 0.5076907873153687 |

| concepts[3].wikidata | https://www.wikidata.org/wiki/Q1161699 |

| concepts[3].display_name | Dynamic range |

| concepts[4].id | https://openalex.org/C103357873 |

| concepts[4].level | 4 |

| concepts[4].score | 0.5025591850280762 |

| concepts[4].wikidata | https://www.wikidata.org/wiki/Q572656 |

| concepts[4].display_name | Switched capacitor |

| concepts[5].id | https://openalex.org/C24326235 |

| concepts[5].level | 1 |

| concepts[5].score | 0.49039435386657715 |

| concepts[5].wikidata | https://www.wikidata.org/wiki/Q126095 |

| concepts[5].display_name | Electronic engineering |

| concepts[6].id | https://openalex.org/C288623 |

| concepts[6].level | 2 |

| concepts[6].score | 0.47441455721855164 |

| concepts[6].wikidata | https://www.wikidata.org/wiki/Q679800 |

| concepts[6].display_name | Nyquist–Shannon sampling theorem |

| concepts[7].id | https://openalex.org/C41008148 |

| concepts[7].level | 0 |

| concepts[7].score | 0.46482518315315247 |

| concepts[7].wikidata | https://www.wikidata.org/wiki/Q21198 |

| concepts[7].display_name | Computer science |

| concepts[8].id | https://openalex.org/C2776310492 |

| concepts[8].level | 3 |

| concepts[8].score | 0.4552761912345886 |

| concepts[8].wikidata | https://www.wikidata.org/wiki/Q3271420 |

| concepts[8].display_name | 12-bit |

| concepts[9].id | https://openalex.org/C173642442 |

| concepts[9].level | 3 |

| concepts[9].score | 0.42605340480804443 |

| concepts[9].wikidata | https://www.wikidata.org/wiki/Q1253346 |

| concepts[9].display_name | Decimation |

| concepts[10].id | https://openalex.org/C74524168 |

| concepts[10].level | 2 |

| concepts[10].score | 0.4133608341217041 |

| concepts[10].wikidata | https://www.wikidata.org/wiki/Q1074539 |

| concepts[10].display_name | Integrated circuit design |

| concepts[11].id | https://openalex.org/C65914096 |

| concepts[11].level | 4 |

| concepts[11].score | 0.4125530421733856 |

| concepts[11].wikidata | https://www.wikidata.org/wiki/Q6273772 |

| concepts[11].display_name | Nyquist rate |

| concepts[12].id | https://openalex.org/C119599485 |

| concepts[12].level | 1 |

| concepts[12].score | 0.28085362911224365 |

| concepts[12].wikidata | https://www.wikidata.org/wiki/Q43035 |

| concepts[12].display_name | Electrical engineering |

| concepts[13].id | https://openalex.org/C127413603 |

| concepts[13].level | 0 |

| concepts[13].score | 0.2244250774383545 |

| concepts[13].wikidata | https://www.wikidata.org/wiki/Q11023 |

| concepts[13].display_name | Engineering |

| concepts[14].id | https://openalex.org/C76155785 |

| concepts[14].level | 1 |

| concepts[14].score | 0.18949151039123535 |

| concepts[14].wikidata | https://www.wikidata.org/wiki/Q418 |

| concepts[14].display_name | Telecommunications |

| concepts[15].id | https://openalex.org/C33923547 |

| concepts[15].level | 0 |

| concepts[15].score | 0.14598709344863892 |

| concepts[15].wikidata | https://www.wikidata.org/wiki/Q395 |

| concepts[15].display_name | Mathematics |

| concepts[16].id | https://openalex.org/C140779682 |

| concepts[16].level | 3 |

| concepts[16].score | 0.14592209458351135 |

| concepts[16].wikidata | https://www.wikidata.org/wiki/Q210868 |

| concepts[16].display_name | Sampling (signal processing) |

| concepts[17].id | https://openalex.org/C2776257435 |

| concepts[17].level | 2 |

| concepts[17].score | 0.12149885296821594 |

| concepts[17].wikidata | https://www.wikidata.org/wiki/Q1576430 |

| concepts[17].display_name | Bandwidth (computing) |

| concepts[18].id | https://openalex.org/C165801399 |

| concepts[18].level | 2 |

| concepts[18].score | 0.10687887668609619 |

| concepts[18].wikidata | https://www.wikidata.org/wiki/Q25428 |

| concepts[18].display_name | Voltage |

| concepts[19].id | https://openalex.org/C2524010 |

| concepts[19].level | 1 |

| concepts[19].score | 0.0 |

| concepts[19].wikidata | https://www.wikidata.org/wiki/Q8087 |

| concepts[19].display_name | Geometry |

| concepts[20].id | https://openalex.org/C94915269 |

| concepts[20].level | 2 |

| concepts[20].score | 0.0 |

| concepts[20].wikidata | https://www.wikidata.org/wiki/Q1834857 |

| concepts[20].display_name | Detector |

| keywords[0].id | https://openalex.org/keywords/cmos |

| keywords[0].score | 0.6665563583374023 |

| keywords[0].display_name | CMOS |

| keywords[1].id | https://openalex.org/keywords/block |

| keywords[1].score | 0.5740953683853149 |

| keywords[1].display_name | Block (permutation group theory) |

| keywords[2].id | https://openalex.org/keywords/capacitor |

| keywords[2].score | 0.5188025832176208 |

| keywords[2].display_name | Capacitor |

| keywords[3].id | https://openalex.org/keywords/dynamic-range |

| keywords[3].score | 0.5076907873153687 |

| keywords[3].display_name | Dynamic range |

| keywords[4].id | https://openalex.org/keywords/switched-capacitor |

| keywords[4].score | 0.5025591850280762 |

| keywords[4].display_name | Switched capacitor |

| keywords[5].id | https://openalex.org/keywords/electronic-engineering |

| keywords[5].score | 0.49039435386657715 |

| keywords[5].display_name | Electronic engineering |

| keywords[6].id | https://openalex.org/keywords/nyquist–shannon-sampling-theorem |

| keywords[6].score | 0.47441455721855164 |

| keywords[6].display_name | Nyquist–Shannon sampling theorem |

| keywords[7].id | https://openalex.org/keywords/computer-science |

| keywords[7].score | 0.46482518315315247 |

| keywords[7].display_name | Computer science |

| keywords[8].id | https://openalex.org/keywords/12-bit |

| keywords[8].score | 0.4552761912345886 |

| keywords[8].display_name | 12-bit |

| keywords[9].id | https://openalex.org/keywords/decimation |

| keywords[9].score | 0.42605340480804443 |

| keywords[9].display_name | Decimation |

| keywords[10].id | https://openalex.org/keywords/integrated-circuit-design |

| keywords[10].score | 0.4133608341217041 |

| keywords[10].display_name | Integrated circuit design |

| keywords[11].id | https://openalex.org/keywords/nyquist-rate |

| keywords[11].score | 0.4125530421733856 |

| keywords[11].display_name | Nyquist rate |

| keywords[12].id | https://openalex.org/keywords/electrical-engineering |

| keywords[12].score | 0.28085362911224365 |

| keywords[12].display_name | Electrical engineering |

| keywords[13].id | https://openalex.org/keywords/engineering |

| keywords[13].score | 0.2244250774383545 |

| keywords[13].display_name | Engineering |

| keywords[14].id | https://openalex.org/keywords/telecommunications |

| keywords[14].score | 0.18949151039123535 |

| keywords[14].display_name | Telecommunications |

| keywords[15].id | https://openalex.org/keywords/mathematics |

| keywords[15].score | 0.14598709344863892 |

| keywords[15].display_name | Mathematics |

| keywords[16].id | https://openalex.org/keywords/sampling |

| keywords[16].score | 0.14592209458351135 |

| keywords[16].display_name | Sampling (signal processing) |

| keywords[17].id | https://openalex.org/keywords/bandwidth |

| keywords[17].score | 0.12149885296821594 |

| keywords[17].display_name | Bandwidth (computing) |

| keywords[18].id | https://openalex.org/keywords/voltage |

| keywords[18].score | 0.10687887668609619 |

| keywords[18].display_name | Voltage |

| language | en |

| locations[0].id | doi:10.36724/2664-066x-2021-7-4-7-11 |

| locations[0].is_oa | True |

| locations[0].source.id | https://openalex.org/S4210177273 |

| locations[0].source.issn | 2664-066X, 2664-0678 |

| locations[0].source.type | journal |

| locations[0].source.is_oa | True |

| locations[0].source.issn_l | 2664-066X |

| locations[0].source.is_core | False |

| locations[0].source.is_in_doaj | False |

| locations[0].source.display_name | SYNCHROINFO JOURNAL |

| locations[0].source.host_organization | https://openalex.org/P4310317908 |

| locations[0].source.host_organization_name | Institute of Radio and Information Systems |

| locations[0].source.host_organization_lineage | https://openalex.org/P4310317908 |

| locations[0].source.host_organization_lineage_names | Institute of Radio and Information Systems |

| locations[0].license | |

| locations[0].pdf_url | https://doi.org/10.36724/2664-066x-2021-7-4-7-11 |

| locations[0].version | publishedVersion |

| locations[0].raw_type | journal-article |

| locations[0].license_id | |

| locations[0].is_accepted | True |

| locations[0].is_published | True |

| locations[0].raw_source_name | SYNCHROINFO JOURNAL |

| locations[0].landing_page_url | http://doi.org/10.36724/2664-066x-2021-7-4-7-11 |

| indexed_in | crossref |

| authorships[0].author.id | https://openalex.org/A5033278524 |

| authorships[0].author.orcid | |

| authorships[0].author.display_name | Mona Safi-Harb |

| authorships[0].countries | CA |

| authorships[0].affiliations[0].institution_ids | https://openalex.org/I5023651 |

| authorships[0].affiliations[0].raw_affiliation_string | Microelectronics & Computer Systems Laboratory, McGill University, Canada, |

| authorships[0].institutions[0].id | https://openalex.org/I5023651 |

| authorships[0].institutions[0].ror | https://ror.org/01pxwe438 |

| authorships[0].institutions[0].type | education |

| authorships[0].institutions[0].lineage | https://openalex.org/I5023651 |

| authorships[0].institutions[0].country_code | CA |

| authorships[0].institutions[0].display_name | McGill University |

| authorships[0].author_position | first |

| authorships[0].raw_author_name | Mona Safi-Harb |

| authorships[0].is_corresponding | False |

| authorships[0].raw_affiliation_strings | Microelectronics & Computer Systems Laboratory, McGill University, Canada, |

| authorships[1].author.id | https://openalex.org/A5083312864 |

| authorships[1].author.orcid | https://orcid.org/0000-0002-4880-0272 |

| authorships[1].author.display_name | Gordon W. Roberts |

| authorships[1].countries | CA |

| authorships[1].affiliations[0].institution_ids | https://openalex.org/I5023651 |

| authorships[1].affiliations[0].raw_affiliation_string | Microelectronics & Computer Systems Laboratory, McGill University, Canada, |

| authorships[1].institutions[0].id | https://openalex.org/I5023651 |

| authorships[1].institutions[0].ror | https://ror.org/01pxwe438 |

| authorships[1].institutions[0].type | education |

| authorships[1].institutions[0].lineage | https://openalex.org/I5023651 |

| authorships[1].institutions[0].country_code | CA |

| authorships[1].institutions[0].display_name | McGill University |

| authorships[1].author_position | last |

| authorships[1].raw_author_name | Gordon W. Roberts |

| authorships[1].is_corresponding | True |

| authorships[1].raw_affiliation_strings | Microelectronics & Computer Systems Laboratory, McGill University, Canada, |

| has_content.pdf | True |

| has_content.grobid_xml | True |

| is_paratext | False |

| open_access.is_oa | True |

| open_access.oa_url | https://doi.org/10.36724/2664-066x-2021-7-4-7-11 |

| open_access.oa_status | diamond |

| open_access.any_repository_has_fulltext | False |

| created_date | 2023-01-19T00:00:00 |

| display_name | A 36 MW, 13 B, 2.1 MS/S MULTI-BIT DS ADC IN 0.18 M DIGITAL CMOS PROCESS USING AN EFFICIENT TOP-DOWN DESIGN METHODOLOGY |

| has_fulltext | True |

| is_retracted | False |

| updated_date | 2025-11-06T03:46:38.306776 |

| primary_topic.id | https://openalex.org/T10323 |

| primary_topic.field.id | https://openalex.org/fields/22 |

| primary_topic.field.display_name | Engineering |

| primary_topic.score | 1.0 |

| primary_topic.domain.id | https://openalex.org/domains/3 |

| primary_topic.domain.display_name | Physical Sciences |

| primary_topic.subfield.id | https://openalex.org/subfields/2204 |

| primary_topic.subfield.display_name | Biomedical Engineering |

| primary_topic.display_name | Analog and Mixed-Signal Circuit Design |

| related_works | https://openalex.org/W2368043784, https://openalex.org/W2576230203, https://openalex.org/W3015557210, https://openalex.org/W2009568739, https://openalex.org/W1570358496, https://openalex.org/W2210983845, https://openalex.org/W2119667497, https://openalex.org/W4235804032, https://openalex.org/W4297933542, https://openalex.org/W2949388829 |

| cited_by_count | 0 |

| locations_count | 1 |

| best_oa_location.id | doi:10.36724/2664-066x-2021-7-4-7-11 |

| best_oa_location.is_oa | True |

| best_oa_location.source.id | https://openalex.org/S4210177273 |

| best_oa_location.source.issn | 2664-066X, 2664-0678 |

| best_oa_location.source.type | journal |

| best_oa_location.source.is_oa | True |

| best_oa_location.source.issn_l | 2664-066X |

| best_oa_location.source.is_core | False |

| best_oa_location.source.is_in_doaj | False |

| best_oa_location.source.display_name | SYNCHROINFO JOURNAL |

| best_oa_location.source.host_organization | https://openalex.org/P4310317908 |

| best_oa_location.source.host_organization_name | Institute of Radio and Information Systems |

| best_oa_location.source.host_organization_lineage | https://openalex.org/P4310317908 |

| best_oa_location.source.host_organization_lineage_names | Institute of Radio and Information Systems |

| best_oa_location.license | |

| best_oa_location.pdf_url | https://doi.org/10.36724/2664-066x-2021-7-4-7-11 |

| best_oa_location.version | publishedVersion |

| best_oa_location.raw_type | journal-article |

| best_oa_location.license_id | |

| best_oa_location.is_accepted | True |

| best_oa_location.is_published | True |

| best_oa_location.raw_source_name | SYNCHROINFO JOURNAL |

| best_oa_location.landing_page_url | http://doi.org/10.36724/2664-066x-2021-7-4-7-11 |

| primary_location.id | doi:10.36724/2664-066x-2021-7-4-7-11 |

| primary_location.is_oa | True |

| primary_location.source.id | https://openalex.org/S4210177273 |

| primary_location.source.issn | 2664-066X, 2664-0678 |

| primary_location.source.type | journal |

| primary_location.source.is_oa | True |

| primary_location.source.issn_l | 2664-066X |

| primary_location.source.is_core | False |

| primary_location.source.is_in_doaj | False |

| primary_location.source.display_name | SYNCHROINFO JOURNAL |

| primary_location.source.host_organization | https://openalex.org/P4310317908 |

| primary_location.source.host_organization_name | Institute of Radio and Information Systems |

| primary_location.source.host_organization_lineage | https://openalex.org/P4310317908 |

| primary_location.source.host_organization_lineage_names | Institute of Radio and Information Systems |

| primary_location.license | |

| primary_location.pdf_url | https://doi.org/10.36724/2664-066x-2021-7-4-7-11 |

| primary_location.version | publishedVersion |

| primary_location.raw_type | journal-article |

| primary_location.license_id | |

| primary_location.is_accepted | True |

| primary_location.is_published | True |

| primary_location.raw_source_name | SYNCHROINFO JOURNAL |

| primary_location.landing_page_url | http://doi.org/10.36724/2664-066x-2021-7-4-7-11 |

| publication_date | 2021-01-01 |

| publication_year | 2021 |

| referenced_works | https://openalex.org/W2385666292, https://openalex.org/W2121882057, https://openalex.org/W1482165582 |

| referenced_works_count | 3 |

| abstract_inverted_index.A | 0 |

| abstract_inverted_index.V | 85 |

| abstract_inverted_index.a | 5, 19, 25, 42, 82 |

| abstract_inverted_index.36 | 89 |

| abstract_inverted_index.50 | 62 |

| abstract_inverted_index.DS | 9 |

| abstract_inverted_index.an | 67, 73 |

| abstract_inverted_index.at | 61 |

| abstract_inverted_index.dB | 69 |

| abstract_inverted_index.in | 29 |

| abstract_inverted_index.is | 13 |

| abstract_inverted_index.mW | 90 |

| abstract_inverted_index.of | 18, 77, 91 |

| abstract_inverted_index.to | 3 |

| abstract_inverted_index.1.8 | 84 |

| abstract_inverted_index.2.1 | 78 |

| abstract_inverted_index.ADC | 10, 28 |

| abstract_inverted_index.The | 15, 34 |

| abstract_inverted_index.and | 54, 87 |

| abstract_inverted_index.are | 57 |

| abstract_inverted_index.for | 72 |

| abstract_inverted_index.the | 30 |

| abstract_inverted_index.(SC) | 7 |

| abstract_inverted_index.81.3 | 68 |

| abstract_inverted_index.MHz, | 63 |

| abstract_inverted_index.MS/s | 79 |

| abstract_inverted_index.When | 59 |

| abstract_inverted_index.fash | 27 |

| abstract_inverted_index.last | 31 |

| abstract_inverted_index.rate | 76 |

| abstract_inverted_index.time | 53 |

| abstract_inverted_index.were | 39 |

| abstract_inverted_index.with | 24 |

| abstract_inverted_index.3-bit | 26 |

| abstract_inverted_index.block | 50 |

| abstract_inverted_index.only. | 33 |

| abstract_inverted_index.range | 71 |

| abstract_inverted_index.stage | 32 |

| abstract_inverted_index.using | 41, 81 |

| abstract_inverted_index.while | 80 |

| abstract_inverted_index.blocks | 37 |

| abstract_inverted_index.design | 4 |

| abstract_inverted_index.method | 2 |

| abstract_inverted_index.output | 74 |

| abstract_inverted_index.power. | 92 |

| abstract_inverted_index.single | 83 |

| abstract_inverted_index.supply | 86 |

| abstract_inverted_index.(2-1-1) | 22 |

| abstract_inverted_index.Nyquist | 75 |

| abstract_inverted_index.between | 47 |

| abstract_inverted_index.circuit | 12, 48 |

| abstract_inverted_index.dynamic | 70 |

| abstract_inverted_index.reveals | 66 |

| abstract_inverted_index.sampled | 60 |

| abstract_inverted_index.building | 36, 49 |

| abstract_inverted_index.consists | 17 |

| abstract_inverted_index.derived. | 58 |

| abstract_inverted_index.designed | 40 |

| abstract_inverted_index.measured | 64 |

| abstract_inverted_index.top-down | 44 |

| abstract_inverted_index.computing | 55 |

| abstract_inverted_index.modulator | 16, 35 |

| abstract_inverted_index.multi-bit | 8 |

| abstract_inverted_index.resources | 56 |

| abstract_inverted_index.Trade-offs | 46 |

| abstract_inverted_index.integrated | 11 |

| abstract_inverted_index.presented. | 14 |

| abstract_inverted_index.systematic | 1, 43 |

| abstract_inverted_index.dissipating | 88 |

| abstract_inverted_index.multi-stage | 21 |

| abstract_inverted_index.performance | 65 |

| abstract_inverted_index.methodology. | 45 |

| abstract_inverted_index.optimization | 52 |

| abstract_inverted_index.architecture, | 23 |

| abstract_inverted_index.fourth-order, | 20 |

| abstract_inverted_index.specifcations | 38 |

| abstract_inverted_index.specifcations, | 51 |

| abstract_inverted_index.switched-capacitor | 6 |

| cited_by_percentile_year | |

| corresponding_author_ids | https://openalex.org/A5083312864 |

| countries_distinct_count | 1 |

| institutions_distinct_count | 2 |

| corresponding_institution_ids | https://openalex.org/I5023651 |

| citation_normalized_percentile.value | 0.2175149 |

| citation_normalized_percentile.is_in_top_1_percent | False |

| citation_normalized_percentile.is_in_top_10_percent | False |