A High-Resistance SOT Device Based Computing-in-Memory Macro With High Sensing Margin and Multi-Bit MAC Operations for AI Edge Inference Article Swipe

Junzhan Liu

,

J.-X. Mi

,

Yang Liu

,

Liang Zhang

,

He Zhang

,

Wang Kang

·

YOU?

·

· 2025

· Open Access

·

· DOI: https://doi.org/10.23919/ics.2025.3567939

YOU?

·

· 2025

· Open Access

·

· DOI: https://doi.org/10.23919/ics.2025.3567939

YOU?

·

· 2025

· Open Access

·

· DOI: https://doi.org/10.23919/ics.2025.3567939

YOU?

·

· 2025

· Open Access

·

· DOI: https://doi.org/10.23919/ics.2025.3567939

Related Topics

Concepts

Metadata

- Type

- article

- Language

- en

- Landing Page

- https://doi.org/10.23919/ics.2025.3567939

- OA Status

- hybrid

- References

- 42

- Related Works

- 10

- OpenAlex ID

- https://openalex.org/W4410153351

All OpenAlex metadata

Raw OpenAlex JSON

- OpenAlex ID

-

https://openalex.org/W4410153351Canonical identifier for this work in OpenAlex

- DOI

-

https://doi.org/10.23919/ics.2025.3567939Digital Object Identifier

- Title

-

A High-Resistance SOT Device Based Computing-in-Memory Macro With High Sensing Margin and Multi-Bit MAC Operations for AI Edge InferenceWork title

- Type

-

articleOpenAlex work type

- Language

-

enPrimary language

- Publication year

-

2025Year of publication

- Publication date

-

2025-05-07Full publication date if available

- Authors

-

Junzhan Liu, J.-X. Mi, Yang Liu, Liang Zhang, He Zhang, Wang KangList of authors in order

- Landing page

-

https://doi.org/10.23919/ics.2025.3567939Publisher landing page

- Open access

-

YesWhether a free full text is available

- OA status

-

hybridOpen access status per OpenAlex

- OA URL

-

https://doi.org/10.23919/ics.2025.3567939Direct OA link when available

- Concepts

-

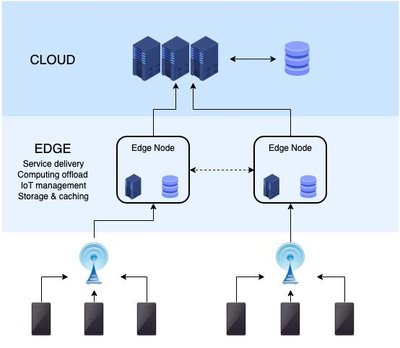

Macro, Margin (machine learning), Inference, Bit (key), Computer science, Enhanced Data Rates for GSM Evolution, Edge computing, Computer hardware, Parallel computing, Artificial intelligence, Computer network, Machine learning, Programming languageTop concepts (fields/topics) attached by OpenAlex

- Cited by

-

0Total citation count in OpenAlex

- References (count)

-

42Number of works referenced by this work

- Related works (count)

-

10Other works algorithmically related by OpenAlex

Full payload

| id | https://openalex.org/W4410153351 |

|---|---|

| doi | https://doi.org/10.23919/ics.2025.3567939 |

| ids.doi | https://doi.org/10.23919/ics.2025.3567939 |

| ids.openalex | https://openalex.org/W4410153351 |

| fwci | 0.0 |

| type | article |

| title | A High-Resistance SOT Device Based Computing-in-Memory Macro With High Sensing Margin and Multi-Bit MAC Operations for AI Edge Inference |

| biblio.issue | 3 |

| biblio.volume | 2 |

| biblio.last_page | 109 |

| biblio.first_page | 102 |

| topics[0].id | https://openalex.org/T10502 |

| topics[0].field.id | https://openalex.org/fields/22 |

| topics[0].field.display_name | Engineering |

| topics[0].score | 0.9991999864578247 |

| topics[0].domain.id | https://openalex.org/domains/3 |

| topics[0].domain.display_name | Physical Sciences |

| topics[0].subfield.id | https://openalex.org/subfields/2208 |

| topics[0].subfield.display_name | Electrical and Electronic Engineering |

| topics[0].display_name | Advanced Memory and Neural Computing |

| topics[1].id | https://openalex.org/T11992 |

| topics[1].field.id | https://openalex.org/fields/22 |

| topics[1].field.display_name | Engineering |

| topics[1].score | 0.989799976348877 |

| topics[1].domain.id | https://openalex.org/domains/3 |

| topics[1].domain.display_name | Physical Sciences |

| topics[1].subfield.id | https://openalex.org/subfields/2208 |

| topics[1].subfield.display_name | Electrical and Electronic Engineering |

| topics[1].display_name | CCD and CMOS Imaging Sensors |

| topics[2].id | https://openalex.org/T12808 |

| topics[2].field.id | https://openalex.org/fields/22 |

| topics[2].field.display_name | Engineering |

| topics[2].score | 0.9884999990463257 |

| topics[2].domain.id | https://openalex.org/domains/3 |

| topics[2].domain.display_name | Physical Sciences |

| topics[2].subfield.id | https://openalex.org/subfields/2208 |

| topics[2].subfield.display_name | Electrical and Electronic Engineering |

| topics[2].display_name | Ferroelectric and Negative Capacitance Devices |

| is_xpac | False |

| apc_list | |

| apc_paid | |

| concepts[0].id | https://openalex.org/C166955791 |

| concepts[0].level | 2 |

| concepts[0].score | 0.7693192958831787 |

| concepts[0].wikidata | https://www.wikidata.org/wiki/Q629579 |

| concepts[0].display_name | Macro |

| concepts[1].id | https://openalex.org/C774472 |

| concepts[1].level | 2 |

| concepts[1].score | 0.7480412721633911 |

| concepts[1].wikidata | https://www.wikidata.org/wiki/Q6760393 |

| concepts[1].display_name | Margin (machine learning) |

| concepts[2].id | https://openalex.org/C2776214188 |

| concepts[2].level | 2 |

| concepts[2].score | 0.7021015882492065 |

| concepts[2].wikidata | https://www.wikidata.org/wiki/Q408386 |

| concepts[2].display_name | Inference |

| concepts[3].id | https://openalex.org/C117011727 |

| concepts[3].level | 2 |

| concepts[3].score | 0.7018537521362305 |

| concepts[3].wikidata | https://www.wikidata.org/wiki/Q1278488 |

| concepts[3].display_name | Bit (key) |

| concepts[4].id | https://openalex.org/C41008148 |

| concepts[4].level | 0 |

| concepts[4].score | 0.6372666954994202 |

| concepts[4].wikidata | https://www.wikidata.org/wiki/Q21198 |

| concepts[4].display_name | Computer science |

| concepts[5].id | https://openalex.org/C162307627 |

| concepts[5].level | 2 |

| concepts[5].score | 0.6230180859565735 |

| concepts[5].wikidata | https://www.wikidata.org/wiki/Q204833 |

| concepts[5].display_name | Enhanced Data Rates for GSM Evolution |

| concepts[6].id | https://openalex.org/C2778456923 |

| concepts[6].level | 3 |

| concepts[6].score | 0.4720381498336792 |

| concepts[6].wikidata | https://www.wikidata.org/wiki/Q5337692 |

| concepts[6].display_name | Edge computing |

| concepts[7].id | https://openalex.org/C9390403 |

| concepts[7].level | 1 |

| concepts[7].score | 0.3534768223762512 |

| concepts[7].wikidata | https://www.wikidata.org/wiki/Q3966 |

| concepts[7].display_name | Computer hardware |

| concepts[8].id | https://openalex.org/C173608175 |

| concepts[8].level | 1 |

| concepts[8].score | 0.3279021978378296 |

| concepts[8].wikidata | https://www.wikidata.org/wiki/Q232661 |

| concepts[8].display_name | Parallel computing |

| concepts[9].id | https://openalex.org/C154945302 |

| concepts[9].level | 1 |

| concepts[9].score | 0.29419180750846863 |

| concepts[9].wikidata | https://www.wikidata.org/wiki/Q11660 |

| concepts[9].display_name | Artificial intelligence |

| concepts[10].id | https://openalex.org/C31258907 |

| concepts[10].level | 1 |

| concepts[10].score | 0.23014798760414124 |

| concepts[10].wikidata | https://www.wikidata.org/wiki/Q1301371 |

| concepts[10].display_name | Computer network |

| concepts[11].id | https://openalex.org/C119857082 |

| concepts[11].level | 1 |

| concepts[11].score | 0.18126347661018372 |

| concepts[11].wikidata | https://www.wikidata.org/wiki/Q2539 |

| concepts[11].display_name | Machine learning |

| concepts[12].id | https://openalex.org/C199360897 |

| concepts[12].level | 1 |

| concepts[12].score | 0.10241737961769104 |

| concepts[12].wikidata | https://www.wikidata.org/wiki/Q9143 |

| concepts[12].display_name | Programming language |

| keywords[0].id | https://openalex.org/keywords/macro |

| keywords[0].score | 0.7693192958831787 |

| keywords[0].display_name | Macro |

| keywords[1].id | https://openalex.org/keywords/margin |

| keywords[1].score | 0.7480412721633911 |

| keywords[1].display_name | Margin (machine learning) |

| keywords[2].id | https://openalex.org/keywords/inference |

| keywords[2].score | 0.7021015882492065 |

| keywords[2].display_name | Inference |

| keywords[3].id | https://openalex.org/keywords/bit |

| keywords[3].score | 0.7018537521362305 |

| keywords[3].display_name | Bit (key) |

| keywords[4].id | https://openalex.org/keywords/computer-science |

| keywords[4].score | 0.6372666954994202 |

| keywords[4].display_name | Computer science |

| keywords[5].id | https://openalex.org/keywords/enhanced-data-rates-for-gsm-evolution |

| keywords[5].score | 0.6230180859565735 |

| keywords[5].display_name | Enhanced Data Rates for GSM Evolution |

| keywords[6].id | https://openalex.org/keywords/edge-computing |

| keywords[6].score | 0.4720381498336792 |

| keywords[6].display_name | Edge computing |

| keywords[7].id | https://openalex.org/keywords/computer-hardware |

| keywords[7].score | 0.3534768223762512 |

| keywords[7].display_name | Computer hardware |

| keywords[8].id | https://openalex.org/keywords/parallel-computing |

| keywords[8].score | 0.3279021978378296 |

| keywords[8].display_name | Parallel computing |

| keywords[9].id | https://openalex.org/keywords/artificial-intelligence |

| keywords[9].score | 0.29419180750846863 |

| keywords[9].display_name | Artificial intelligence |

| keywords[10].id | https://openalex.org/keywords/computer-network |

| keywords[10].score | 0.23014798760414124 |

| keywords[10].display_name | Computer network |

| keywords[11].id | https://openalex.org/keywords/machine-learning |

| keywords[11].score | 0.18126347661018372 |

| keywords[11].display_name | Machine learning |

| keywords[12].id | https://openalex.org/keywords/programming-language |

| keywords[12].score | 0.10241737961769104 |

| keywords[12].display_name | Programming language |

| language | en |

| locations[0].id | doi:10.23919/ics.2025.3567939 |

| locations[0].is_oa | True |

| locations[0].source.id | https://openalex.org/S5407042419 |

| locations[0].source.issn | 2995-1968, 2995-1976 |

| locations[0].source.type | journal |

| locations[0].source.is_oa | False |

| locations[0].source.issn_l | 2995-1968 |

| locations[0].source.is_core | False |

| locations[0].source.is_in_doaj | False |

| locations[0].source.display_name | Integrated Circuits and Systems |

| locations[0].source.host_organization | |

| locations[0].source.host_organization_name | |

| locations[0].license | cc-by |

| locations[0].pdf_url | |

| locations[0].version | publishedVersion |

| locations[0].raw_type | journal-article |

| locations[0].license_id | https://openalex.org/licenses/cc-by |

| locations[0].is_accepted | True |

| locations[0].is_published | True |

| locations[0].raw_source_name | Integrated Circuits and Systems |

| locations[0].landing_page_url | https://doi.org/10.23919/ics.2025.3567939 |

| indexed_in | crossref |

| authorships[0].author.id | https://openalex.org/A5011086884 |

| authorships[0].author.orcid | https://orcid.org/0009-0008-0295-5309 |

| authorships[0].author.display_name | Junzhan Liu |

| authorships[0].countries | CN |

| authorships[0].affiliations[0].institution_ids | https://openalex.org/I82880672 |

| authorships[0].affiliations[0].raw_affiliation_string | School of Integrated Circuit Science and Engineering, Beihang University, Beijing, China |

| authorships[0].institutions[0].id | https://openalex.org/I82880672 |

| authorships[0].institutions[0].ror | https://ror.org/00wk2mp56 |

| authorships[0].institutions[0].type | education |

| authorships[0].institutions[0].lineage | https://openalex.org/I82880672 |

| authorships[0].institutions[0].country_code | CN |

| authorships[0].institutions[0].display_name | Beihang University |

| authorships[0].author_position | first |

| authorships[0].raw_author_name | Junzhan Liu |

| authorships[0].is_corresponding | False |

| authorships[0].raw_affiliation_strings | School of Integrated Circuit Science and Engineering, Beihang University, Beijing, China |

| authorships[1].author.id | https://openalex.org/A5055567380 |

| authorships[1].author.orcid | |

| authorships[1].author.display_name | J.-X. Mi |

| authorships[1].countries | CN |

| authorships[1].affiliations[0].institution_ids | https://openalex.org/I82880672 |

| authorships[1].affiliations[0].raw_affiliation_string | School of Integrated Circuit Science and Engineering, Beihang University, Beijing, China |

| authorships[1].institutions[0].id | https://openalex.org/I82880672 |

| authorships[1].institutions[0].ror | https://ror.org/00wk2mp56 |

| authorships[1].institutions[0].type | education |

| authorships[1].institutions[0].lineage | https://openalex.org/I82880672 |

| authorships[1].institutions[0].country_code | CN |

| authorships[1].institutions[0].display_name | Beihang University |

| authorships[1].author_position | middle |

| authorships[1].raw_author_name | Jinyao Mi |

| authorships[1].is_corresponding | False |

| authorships[1].raw_affiliation_strings | School of Integrated Circuit Science and Engineering, Beihang University, Beijing, China |

| authorships[2].author.id | https://openalex.org/A5100355929 |

| authorships[2].author.orcid | https://orcid.org/0000-0002-5611-5881 |

| authorships[2].author.display_name | Yang Liu |

| authorships[2].countries | CN |

| authorships[2].affiliations[0].institution_ids | https://openalex.org/I82880672 |

| authorships[2].affiliations[0].raw_affiliation_string | School of Electronic Information Engineering, Beihang University, Beijing, China |

| authorships[2].institutions[0].id | https://openalex.org/I82880672 |

| authorships[2].institutions[0].ror | https://ror.org/00wk2mp56 |

| authorships[2].institutions[0].type | education |

| authorships[2].institutions[0].lineage | https://openalex.org/I82880672 |

| authorships[2].institutions[0].country_code | CN |

| authorships[2].institutions[0].display_name | Beihang University |

| authorships[2].author_position | middle |

| authorships[2].raw_author_name | Yang Liu |

| authorships[2].is_corresponding | False |

| authorships[2].raw_affiliation_strings | School of Electronic Information Engineering, Beihang University, Beijing, China |

| authorships[3].author.id | https://openalex.org/A5100425160 |

| authorships[3].author.orcid | https://orcid.org/0000-0001-9233-5972 |

| authorships[3].author.display_name | Liang Zhang |

| authorships[3].countries | CN |

| authorships[3].affiliations[0].institution_ids | https://openalex.org/I82880672 |

| authorships[3].affiliations[0].raw_affiliation_string | School of Integrated Circuit Science and Engineering, Beihang University, Beijing, China |

| authorships[3].institutions[0].id | https://openalex.org/I82880672 |

| authorships[3].institutions[0].ror | https://ror.org/00wk2mp56 |

| authorships[3].institutions[0].type | education |

| authorships[3].institutions[0].lineage | https://openalex.org/I82880672 |

| authorships[3].institutions[0].country_code | CN |

| authorships[3].institutions[0].display_name | Beihang University |

| authorships[3].author_position | middle |

| authorships[3].raw_author_name | Liang Zhang |

| authorships[3].is_corresponding | False |

| authorships[3].raw_affiliation_strings | School of Integrated Circuit Science and Engineering, Beihang University, Beijing, China |

| authorships[4].author.id | https://openalex.org/A5100420104 |

| authorships[4].author.orcid | https://orcid.org/0000-0001-9262-3106 |

| authorships[4].author.display_name | He Zhang |

| authorships[4].countries | CN |

| authorships[4].affiliations[0].institution_ids | https://openalex.org/I82880672 |

| authorships[4].affiliations[0].raw_affiliation_string | School of Integrated Circuit Science and Engineering, Beihang University, Beijing, China |

| authorships[4].institutions[0].id | https://openalex.org/I82880672 |

| authorships[4].institutions[0].ror | https://ror.org/00wk2mp56 |

| authorships[4].institutions[0].type | education |

| authorships[4].institutions[0].lineage | https://openalex.org/I82880672 |

| authorships[4].institutions[0].country_code | CN |

| authorships[4].institutions[0].display_name | Beihang University |

| authorships[4].author_position | middle |

| authorships[4].raw_author_name | He Zhang |

| authorships[4].is_corresponding | False |

| authorships[4].raw_affiliation_strings | School of Integrated Circuit Science and Engineering, Beihang University, Beijing, China |

| authorships[5].author.id | https://openalex.org/A5100381646 |

| authorships[5].author.orcid | https://orcid.org/0000-0002-3169-6034 |

| authorships[5].author.display_name | Wang Kang |

| authorships[5].countries | CN |

| authorships[5].affiliations[0].institution_ids | https://openalex.org/I82880672 |

| authorships[5].affiliations[0].raw_affiliation_string | School of Integrated Circuit Science and Engineering, Beihang University, Beijing, China |

| authorships[5].institutions[0].id | https://openalex.org/I82880672 |

| authorships[5].institutions[0].ror | https://ror.org/00wk2mp56 |

| authorships[5].institutions[0].type | education |

| authorships[5].institutions[0].lineage | https://openalex.org/I82880672 |

| authorships[5].institutions[0].country_code | CN |

| authorships[5].institutions[0].display_name | Beihang University |

| authorships[5].author_position | last |

| authorships[5].raw_author_name | Wang Kang |

| authorships[5].is_corresponding | False |

| authorships[5].raw_affiliation_strings | School of Integrated Circuit Science and Engineering, Beihang University, Beijing, China |

| has_content.pdf | False |

| has_content.grobid_xml | False |

| is_paratext | False |

| open_access.is_oa | True |

| open_access.oa_url | https://doi.org/10.23919/ics.2025.3567939 |

| open_access.oa_status | hybrid |

| open_access.any_repository_has_fulltext | False |

| created_date | 2025-10-10T00:00:00 |

| display_name | A High-Resistance SOT Device Based Computing-in-Memory Macro With High Sensing Margin and Multi-Bit MAC Operations for AI Edge Inference |

| has_fulltext | False |

| is_retracted | False |

| updated_date | 2025-11-06T03:46:38.306776 |

| primary_topic.id | https://openalex.org/T10502 |

| primary_topic.field.id | https://openalex.org/fields/22 |

| primary_topic.field.display_name | Engineering |

| primary_topic.score | 0.9991999864578247 |

| primary_topic.domain.id | https://openalex.org/domains/3 |

| primary_topic.domain.display_name | Physical Sciences |

| primary_topic.subfield.id | https://openalex.org/subfields/2208 |

| primary_topic.subfield.display_name | Electrical and Electronic Engineering |

| primary_topic.display_name | Advanced Memory and Neural Computing |

| related_works | https://openalex.org/W2030816003, https://openalex.org/W4327546585, https://openalex.org/W4239992647, https://openalex.org/W2150013480, https://openalex.org/W1554458299, https://openalex.org/W81423522, https://openalex.org/W1509860481, https://openalex.org/W2488264085, https://openalex.org/W2076325756, https://openalex.org/W4386206750 |

| cited_by_count | 0 |

| locations_count | 1 |

| best_oa_location.id | doi:10.23919/ics.2025.3567939 |

| best_oa_location.is_oa | True |

| best_oa_location.source.id | https://openalex.org/S5407042419 |

| best_oa_location.source.issn | 2995-1968, 2995-1976 |

| best_oa_location.source.type | journal |

| best_oa_location.source.is_oa | False |

| best_oa_location.source.issn_l | 2995-1968 |

| best_oa_location.source.is_core | False |

| best_oa_location.source.is_in_doaj | False |

| best_oa_location.source.display_name | Integrated Circuits and Systems |

| best_oa_location.source.host_organization | |

| best_oa_location.source.host_organization_name | |

| best_oa_location.license | cc-by |

| best_oa_location.pdf_url | |

| best_oa_location.version | publishedVersion |

| best_oa_location.raw_type | journal-article |

| best_oa_location.license_id | https://openalex.org/licenses/cc-by |

| best_oa_location.is_accepted | True |

| best_oa_location.is_published | True |

| best_oa_location.raw_source_name | Integrated Circuits and Systems |

| best_oa_location.landing_page_url | https://doi.org/10.23919/ics.2025.3567939 |

| primary_location.id | doi:10.23919/ics.2025.3567939 |

| primary_location.is_oa | True |

| primary_location.source.id | https://openalex.org/S5407042419 |

| primary_location.source.issn | 2995-1968, 2995-1976 |

| primary_location.source.type | journal |

| primary_location.source.is_oa | False |

| primary_location.source.issn_l | 2995-1968 |

| primary_location.source.is_core | False |

| primary_location.source.is_in_doaj | False |

| primary_location.source.display_name | Integrated Circuits and Systems |

| primary_location.source.host_organization | |

| primary_location.source.host_organization_name | |

| primary_location.license | cc-by |

| primary_location.pdf_url | |

| primary_location.version | publishedVersion |

| primary_location.raw_type | journal-article |

| primary_location.license_id | https://openalex.org/licenses/cc-by |

| primary_location.is_accepted | True |

| primary_location.is_published | True |

| primary_location.raw_source_name | Integrated Circuits and Systems |

| primary_location.landing_page_url | https://doi.org/10.23919/ics.2025.3567939 |

| publication_date | 2025-05-07 |

| publication_year | 2025 |

| referenced_works | https://openalex.org/W2919115771, https://openalex.org/W4246193833, https://openalex.org/W3117804044, https://openalex.org/W1999085092, https://openalex.org/W4388626384, https://openalex.org/W2969812992, https://openalex.org/W3174208823, https://openalex.org/W4391014324, https://openalex.org/W4403063814, https://openalex.org/W3015982917, https://openalex.org/W2966524683, https://openalex.org/W4293261874, https://openalex.org/W3159353913, https://openalex.org/W2790511620, https://openalex.org/W3164913974, https://openalex.org/W4403278665, https://openalex.org/W4391892592, https://openalex.org/W4401880495, https://openalex.org/W4376131445, https://openalex.org/W4364860217, https://openalex.org/W3157026464, https://openalex.org/W3136336547, https://openalex.org/W4310584033, https://openalex.org/W3009326909, https://openalex.org/W2588666075, https://openalex.org/W2588236721, https://openalex.org/W4360607286, https://openalex.org/W2944473316, https://openalex.org/W4286571786, https://openalex.org/W4390357717, https://openalex.org/W4226518647, https://openalex.org/W3209341468, https://openalex.org/W4387411178, https://openalex.org/W4404035840, https://openalex.org/W4205230840, https://openalex.org/W3201969459, https://openalex.org/W4390097232, https://openalex.org/W4312751404, https://openalex.org/W4386159720, https://openalex.org/W4393178071, https://openalex.org/W4214757564, https://openalex.org/W3107913576 |

| referenced_works_count | 42 |

| abstract_inverted_index | |

| cited_by_percentile_year | |

| countries_distinct_count | 1 |

| institutions_distinct_count | 6 |

| citation_normalized_percentile.value | 0.15551222 |

| citation_normalized_percentile.is_in_top_1_percent | False |

| citation_normalized_percentile.is_in_top_10_percent | False |