An unprotected RISC-V Soft-core processor on an SRAM FPGA: Is it as bad as it sounds? Article Swipe

YOU?

·

· 2023

· Open Access

·

· DOI: https://doi.org/10.1109/ets56758.2023.10174076

YOU?

·

· 2023

· Open Access

·

· DOI: https://doi.org/10.1109/ets56758.2023.10174076

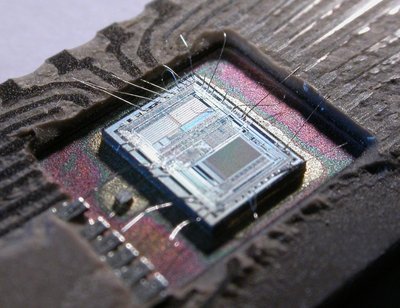

Fast development, low cost, and reconfigurability are becoming critical factors for aerospace applications, making SRAM FPGAs attractive. However, SRAM FPGAs are prone to errors in the user and on the configuration bits. For their correct functioning, they must be capable of withstanding failures without sacrificing much performance. When adjusting a soft core for these applications, it is essential to know where redundancies are necessary, to avoid unnecessary overhead. We characterize the reliability of an unprotected RISC-V microcontroller using an accelerated neutron beam. Our investigation shows that, for our chosen benchmark and processor, the user data in the memory banks is the leading cause of the total number of errors in the application. By reversing the benchmark operations, we could root cause the origin of the observed errors and found that most of the data corruption detected during the runs stem from previously corrupt input data or from output data that were corrupted while transmitting.

Related Topics

- Type

- article

- Language

- en

- Landing Page

- https://doi.org/10.1109/ets56758.2023.10174076

- OA Status

- gold

- Cited By

- 3

- References

- 20

- Related Works

- 10

- OpenAlex ID

- https://openalex.org/W4384009476

Raw OpenAlex JSON

- OpenAlex ID

-

https://openalex.org/W4384009476Canonical identifier for this work in OpenAlex

- DOI

-

https://doi.org/10.1109/ets56758.2023.10174076Digital Object Identifier

- Title

-

An unprotected RISC-V Soft-core processor on an SRAM FPGA: Is it as bad as it sounds?Work title

- Type

-

articleOpenAlex work type

- Language

-

enPrimary language

- Publication year

-

2023Year of publication

- Publication date

-

2023-05-22Full publication date if available

- Authors

-

Bruno Endres Forlin, Wouter van Huffelen, Carlo Cazzaniga, Paolo Rech, Nikolaos Alachiotis, Marco OttaviList of authors in order

- Landing page

-

https://doi.org/10.1109/ets56758.2023.10174076Publisher landing page

- Open access

-

YesWhether a free full text is available

- OA status

-

goldOpen access status per OpenAlex

- OA URL

-

https://research.utwente.nl/en/publications/021d716d-f5e8-470b-9733-290911607378Direct OA link when available

- Concepts

-

Static random-access memory, Computer science, Reconfigurability, Embedded system, Benchmark (surveying), Field-programmable gate array, Multi-core processor, Overhead (engineering), Microcontroller, Reliability (semiconductor), Computer hardware, Parallel computing, Operating system, Power (physics), Geography, Quantum mechanics, Geodesy, PhysicsTop concepts (fields/topics) attached by OpenAlex

- Cited by

-

3Total citation count in OpenAlex

- Citations by year (recent)

-

2025: 2, 2024: 1Per-year citation counts (last 5 years)

- References (count)

-

20Number of works referenced by this work

- Related works (count)

-

10Other works algorithmically related by OpenAlex

Full payload

| id | https://openalex.org/W4384009476 |

|---|---|

| doi | https://doi.org/10.1109/ets56758.2023.10174076 |

| ids.doi | https://doi.org/10.1109/ets56758.2023.10174076 |

| ids.openalex | https://openalex.org/W4384009476 |

| fwci | 0.49765169 |

| type | article |

| title | An unprotected RISC-V Soft-core processor on an SRAM FPGA: Is it as bad as it sounds? |

| biblio.issue | |

| biblio.volume | |

| biblio.last_page | 6 |

| biblio.first_page | 1 |

| topics[0].id | https://openalex.org/T11005 |

| topics[0].field.id | https://openalex.org/fields/22 |

| topics[0].field.display_name | Engineering |

| topics[0].score | 1.0 |

| topics[0].domain.id | https://openalex.org/domains/3 |

| topics[0].domain.display_name | Physical Sciences |

| topics[0].subfield.id | https://openalex.org/subfields/2208 |

| topics[0].subfield.display_name | Electrical and Electronic Engineering |

| topics[0].display_name | Radiation Effects in Electronics |

| topics[1].id | https://openalex.org/T11032 |

| topics[1].field.id | https://openalex.org/fields/17 |

| topics[1].field.display_name | Computer Science |

| topics[1].score | 0.9958000183105469 |

| topics[1].domain.id | https://openalex.org/domains/3 |

| topics[1].domain.display_name | Physical Sciences |

| topics[1].subfield.id | https://openalex.org/subfields/1708 |

| topics[1].subfield.display_name | Hardware and Architecture |

| topics[1].display_name | VLSI and Analog Circuit Testing |

| topics[2].id | https://openalex.org/T11424 |

| topics[2].field.id | https://openalex.org/fields/17 |

| topics[2].field.display_name | Computer Science |

| topics[2].score | 0.9954000115394592 |

| topics[2].domain.id | https://openalex.org/domains/3 |

| topics[2].domain.display_name | Physical Sciences |

| topics[2].subfield.id | https://openalex.org/subfields/1702 |

| topics[2].subfield.display_name | Artificial Intelligence |

| topics[2].display_name | Security and Verification in Computing |

| is_xpac | False |

| apc_list | |

| apc_paid | |

| concepts[0].id | https://openalex.org/C68043766 |

| concepts[0].level | 2 |

| concepts[0].score | 0.8198685646057129 |

| concepts[0].wikidata | https://www.wikidata.org/wiki/Q267416 |

| concepts[0].display_name | Static random-access memory |

| concepts[1].id | https://openalex.org/C41008148 |

| concepts[1].level | 0 |

| concepts[1].score | 0.71944659948349 |

| concepts[1].wikidata | https://www.wikidata.org/wiki/Q21198 |

| concepts[1].display_name | Computer science |

| concepts[2].id | https://openalex.org/C2780149590 |

| concepts[2].level | 2 |

| concepts[2].score | 0.7091898918151855 |

| concepts[2].wikidata | https://www.wikidata.org/wiki/Q7302742 |

| concepts[2].display_name | Reconfigurability |

| concepts[3].id | https://openalex.org/C149635348 |

| concepts[3].level | 1 |

| concepts[3].score | 0.6416035294532776 |

| concepts[3].wikidata | https://www.wikidata.org/wiki/Q193040 |

| concepts[3].display_name | Embedded system |

| concepts[4].id | https://openalex.org/C185798385 |

| concepts[4].level | 2 |

| concepts[4].score | 0.6136192083358765 |

| concepts[4].wikidata | https://www.wikidata.org/wiki/Q1161707 |

| concepts[4].display_name | Benchmark (surveying) |

| concepts[5].id | https://openalex.org/C42935608 |

| concepts[5].level | 2 |

| concepts[5].score | 0.5878021717071533 |

| concepts[5].wikidata | https://www.wikidata.org/wiki/Q190411 |

| concepts[5].display_name | Field-programmable gate array |

| concepts[6].id | https://openalex.org/C78766204 |

| concepts[6].level | 2 |

| concepts[6].score | 0.5659829378128052 |

| concepts[6].wikidata | https://www.wikidata.org/wiki/Q555032 |

| concepts[6].display_name | Multi-core processor |

| concepts[7].id | https://openalex.org/C2779960059 |

| concepts[7].level | 2 |

| concepts[7].score | 0.5203251838684082 |

| concepts[7].wikidata | https://www.wikidata.org/wiki/Q7113681 |

| concepts[7].display_name | Overhead (engineering) |

| concepts[8].id | https://openalex.org/C173018170 |

| concepts[8].level | 2 |

| concepts[8].score | 0.4706170856952667 |

| concepts[8].wikidata | https://www.wikidata.org/wiki/Q165678 |

| concepts[8].display_name | Microcontroller |

| concepts[9].id | https://openalex.org/C43214815 |

| concepts[9].level | 3 |

| concepts[9].score | 0.4324607849121094 |

| concepts[9].wikidata | https://www.wikidata.org/wiki/Q7310987 |

| concepts[9].display_name | Reliability (semiconductor) |

| concepts[10].id | https://openalex.org/C9390403 |

| concepts[10].level | 1 |

| concepts[10].score | 0.3972488343715668 |

| concepts[10].wikidata | https://www.wikidata.org/wiki/Q3966 |

| concepts[10].display_name | Computer hardware |

| concepts[11].id | https://openalex.org/C173608175 |

| concepts[11].level | 1 |

| concepts[11].score | 0.27565330266952515 |

| concepts[11].wikidata | https://www.wikidata.org/wiki/Q232661 |

| concepts[11].display_name | Parallel computing |

| concepts[12].id | https://openalex.org/C111919701 |

| concepts[12].level | 1 |

| concepts[12].score | 0.1525384783744812 |

| concepts[12].wikidata | https://www.wikidata.org/wiki/Q9135 |

| concepts[12].display_name | Operating system |

| concepts[13].id | https://openalex.org/C163258240 |

| concepts[13].level | 2 |

| concepts[13].score | 0.09377998113632202 |

| concepts[13].wikidata | https://www.wikidata.org/wiki/Q25342 |

| concepts[13].display_name | Power (physics) |

| concepts[14].id | https://openalex.org/C205649164 |

| concepts[14].level | 0 |

| concepts[14].score | 0.0 |

| concepts[14].wikidata | https://www.wikidata.org/wiki/Q1071 |

| concepts[14].display_name | Geography |

| concepts[15].id | https://openalex.org/C62520636 |

| concepts[15].level | 1 |

| concepts[15].score | 0.0 |

| concepts[15].wikidata | https://www.wikidata.org/wiki/Q944 |

| concepts[15].display_name | Quantum mechanics |

| concepts[16].id | https://openalex.org/C13280743 |

| concepts[16].level | 1 |

| concepts[16].score | 0.0 |

| concepts[16].wikidata | https://www.wikidata.org/wiki/Q131089 |

| concepts[16].display_name | Geodesy |

| concepts[17].id | https://openalex.org/C121332964 |

| concepts[17].level | 0 |

| concepts[17].score | 0.0 |

| concepts[17].wikidata | https://www.wikidata.org/wiki/Q413 |

| concepts[17].display_name | Physics |

| keywords[0].id | https://openalex.org/keywords/static-random-access-memory |

| keywords[0].score | 0.8198685646057129 |

| keywords[0].display_name | Static random-access memory |

| keywords[1].id | https://openalex.org/keywords/computer-science |

| keywords[1].score | 0.71944659948349 |

| keywords[1].display_name | Computer science |

| keywords[2].id | https://openalex.org/keywords/reconfigurability |

| keywords[2].score | 0.7091898918151855 |

| keywords[2].display_name | Reconfigurability |

| keywords[3].id | https://openalex.org/keywords/embedded-system |

| keywords[3].score | 0.6416035294532776 |

| keywords[3].display_name | Embedded system |

| keywords[4].id | https://openalex.org/keywords/benchmark |

| keywords[4].score | 0.6136192083358765 |

| keywords[4].display_name | Benchmark (surveying) |

| keywords[5].id | https://openalex.org/keywords/field-programmable-gate-array |

| keywords[5].score | 0.5878021717071533 |

| keywords[5].display_name | Field-programmable gate array |

| keywords[6].id | https://openalex.org/keywords/multi-core-processor |

| keywords[6].score | 0.5659829378128052 |

| keywords[6].display_name | Multi-core processor |

| keywords[7].id | https://openalex.org/keywords/overhead |

| keywords[7].score | 0.5203251838684082 |

| keywords[7].display_name | Overhead (engineering) |

| keywords[8].id | https://openalex.org/keywords/microcontroller |

| keywords[8].score | 0.4706170856952667 |

| keywords[8].display_name | Microcontroller |

| keywords[9].id | https://openalex.org/keywords/reliability |

| keywords[9].score | 0.4324607849121094 |

| keywords[9].display_name | Reliability (semiconductor) |

| keywords[10].id | https://openalex.org/keywords/computer-hardware |

| keywords[10].score | 0.3972488343715668 |

| keywords[10].display_name | Computer hardware |

| keywords[11].id | https://openalex.org/keywords/parallel-computing |

| keywords[11].score | 0.27565330266952515 |

| keywords[11].display_name | Parallel computing |

| keywords[12].id | https://openalex.org/keywords/operating-system |

| keywords[12].score | 0.1525384783744812 |

| keywords[12].display_name | Operating system |

| keywords[13].id | https://openalex.org/keywords/power |

| keywords[13].score | 0.09377998113632202 |

| keywords[13].display_name | Power (physics) |

| language | en |

| locations[0].id | doi:10.1109/ets56758.2023.10174076 |

| locations[0].is_oa | False |

| locations[0].source | |

| locations[0].license | |

| locations[0].pdf_url | |

| locations[0].version | publishedVersion |

| locations[0].raw_type | proceedings-article |

| locations[0].license_id | |

| locations[0].is_accepted | True |

| locations[0].is_published | True |

| locations[0].raw_source_name | 2023 IEEE European Test Symposium (ETS) |

| locations[0].landing_page_url | https://doi.org/10.1109/ets56758.2023.10174076 |

| locations[1].id | pmh:oai:art.torvergata.it:2108/384185 |

| locations[1].is_oa | False |

| locations[1].source.id | https://openalex.org/S4306400993 |

| locations[1].source.issn | |

| locations[1].source.type | repository |

| locations[1].source.is_oa | False |

| locations[1].source.issn_l | |

| locations[1].source.is_core | False |

| locations[1].source.is_in_doaj | False |

| locations[1].source.display_name | Cineca Institutional Research Information System (Tor Vergata University) |

| locations[1].source.host_organization | https://openalex.org/I116067653 |

| locations[1].source.host_organization_name | University of Rome Tor Vergata |

| locations[1].source.host_organization_lineage | https://openalex.org/I116067653 |

| locations[1].license | |

| locations[1].pdf_url | |

| locations[1].version | submittedVersion |

| locations[1].raw_type | info:eu-repo/semantics/conferenceObject |

| locations[1].license_id | |

| locations[1].is_accepted | False |

| locations[1].is_published | False |

| locations[1].raw_source_name | |

| locations[1].landing_page_url | https://hdl.handle.net/2108/384185 |

| locations[2].id | pmh:oai:iris.unitn.it:11572/434272 |

| locations[2].is_oa | False |

| locations[2].source.id | https://openalex.org/S4306401913 |

| locations[2].source.issn | |

| locations[2].source.type | repository |

| locations[2].source.is_oa | False |

| locations[2].source.issn_l | |

| locations[2].source.is_core | False |

| locations[2].source.is_in_doaj | False |

| locations[2].source.display_name | Institutional Research Information System (Università degli Studi di Trento) |

| locations[2].source.host_organization | https://openalex.org/I193223587 |

| locations[2].source.host_organization_name | University of Trento |

| locations[2].source.host_organization_lineage | https://openalex.org/I193223587 |

| locations[2].license | |

| locations[2].pdf_url | |

| locations[2].version | submittedVersion |

| locations[2].raw_type | info:eu-repo/semantics/conferenceObject |

| locations[2].license_id | |

| locations[2].is_accepted | False |

| locations[2].is_published | False |

| locations[2].raw_source_name | |

| locations[2].landing_page_url | https://hdl.handle.net/11572/434272 |

| locations[3].id | pmh:oai:purl.org/net/epubs:work/54230565 |

| locations[3].is_oa | False |

| locations[3].source | |

| locations[3].license | |

| locations[3].pdf_url | |

| locations[3].version | submittedVersion |

| locations[3].raw_type | Text |

| locations[3].license_id | |

| locations[3].is_accepted | False |

| locations[3].is_published | False |

| locations[3].raw_source_name | |

| locations[3].landing_page_url | http://purl.org/net/epubs/work/54230565 |

| locations[4].id | pmh:oai:ris.utwente.nl:openaire_cris_publications/021d716d-f5e8-470b-9733-290911607378 |

| locations[4].is_oa | True |

| locations[4].source | |

| locations[4].license | other-oa |

| locations[4].pdf_url | |

| locations[4].version | submittedVersion |

| locations[4].raw_type | contributionToPeriodical |

| locations[4].license_id | https://openalex.org/licenses/other-oa |

| locations[4].is_accepted | False |

| locations[4].is_published | False |

| locations[4].raw_source_name | Forlin , B E , van Huffelen , W , Cazzaniga , C , Rech , P , Alachiotis , N & Ottavi , M 2023 , An unprotected RISC-V Soft-core processor on an SRAM FPGA : Is it as bad as it sounds? in Proceedings - 2023 IEEE European Test Symposium, ETS 2023 . Proceedings IEEE European Test Symposium (ETS) , vol. 2023 , IEEE , Piscataway, NJ , 28th IEEE European Test Symposium, ETS 2023 , Venice , Italy , 22/05/23 . https://doi.org/10.1109/ETS56758.2023.10174076 |

| locations[4].landing_page_url | https://research.utwente.nl/en/publications/021d716d-f5e8-470b-9733-290911607378 |

| indexed_in | crossref |

| authorships[0].author.id | https://openalex.org/A5023084270 |

| authorships[0].author.orcid | |

| authorships[0].author.display_name | Bruno Endres Forlin |

| authorships[0].countries | NL |

| authorships[0].affiliations[0].institution_ids | https://openalex.org/I94624287 |

| authorships[0].affiliations[0].raw_affiliation_string | University of Twente, The Netherlands |

| authorships[0].institutions[0].id | https://openalex.org/I94624287 |

| authorships[0].institutions[0].ror | https://ror.org/006hf6230 |

| authorships[0].institutions[0].type | education |

| authorships[0].institutions[0].lineage | https://openalex.org/I94624287 |

| authorships[0].institutions[0].country_code | NL |

| authorships[0].institutions[0].display_name | University of Twente |

| authorships[0].author_position | first |

| authorships[0].raw_author_name | Bruno Endres Forlin |

| authorships[0].is_corresponding | False |

| authorships[0].raw_affiliation_strings | University of Twente, The Netherlands |

| authorships[1].author.id | https://openalex.org/A5092451041 |

| authorships[1].author.orcid | |

| authorships[1].author.display_name | Wouter van Huffelen |

| authorships[1].countries | NL |

| authorships[1].affiliations[0].institution_ids | https://openalex.org/I94624287 |

| authorships[1].affiliations[0].raw_affiliation_string | University of Twente, The Netherlands |

| authorships[1].institutions[0].id | https://openalex.org/I94624287 |

| authorships[1].institutions[0].ror | https://ror.org/006hf6230 |

| authorships[1].institutions[0].type | education |

| authorships[1].institutions[0].lineage | https://openalex.org/I94624287 |

| authorships[1].institutions[0].country_code | NL |

| authorships[1].institutions[0].display_name | University of Twente |

| authorships[1].author_position | middle |

| authorships[1].raw_author_name | Wouter van Huffelen |

| authorships[1].is_corresponding | False |

| authorships[1].raw_affiliation_strings | University of Twente, The Netherlands |

| authorships[2].author.id | https://openalex.org/A5011899281 |

| authorships[2].author.orcid | https://orcid.org/0000-0002-3110-0253 |

| authorships[2].author.display_name | Carlo Cazzaniga |

| authorships[2].countries | GB |

| authorships[2].affiliations[0].institution_ids | https://openalex.org/I1286704778 |

| authorships[2].affiliations[0].raw_affiliation_string | Rutherford Appleton Laboratory, UK |

| authorships[2].institutions[0].id | https://openalex.org/I1286704778 |

| authorships[2].institutions[0].ror | https://ror.org/03gq8fr08 |

| authorships[2].institutions[0].type | facility |

| authorships[2].institutions[0].lineage | https://openalex.org/I1286704778, https://openalex.org/I162524378, https://openalex.org/I4210087105 |

| authorships[2].institutions[0].country_code | GB |

| authorships[2].institutions[0].display_name | Rutherford Appleton Laboratory |

| authorships[2].author_position | middle |

| authorships[2].raw_author_name | Carlo Cazzaniga |

| authorships[2].is_corresponding | False |

| authorships[2].raw_affiliation_strings | Rutherford Appleton Laboratory, UK |

| authorships[3].author.id | https://openalex.org/A5054264208 |

| authorships[3].author.orcid | |

| authorships[3].author.display_name | Paolo Rech |

| authorships[3].countries | IT |

| authorships[3].affiliations[0].institution_ids | https://openalex.org/I193223587 |

| authorships[3].affiliations[0].raw_affiliation_string | Univeristy of Trento, Italy |

| authorships[3].institutions[0].id | https://openalex.org/I193223587 |

| authorships[3].institutions[0].ror | https://ror.org/05trd4x28 |

| authorships[3].institutions[0].type | education |

| authorships[3].institutions[0].lineage | https://openalex.org/I193223587 |

| authorships[3].institutions[0].country_code | IT |

| authorships[3].institutions[0].display_name | University of Trento |

| authorships[3].author_position | middle |

| authorships[3].raw_author_name | Paolo Rech |

| authorships[3].is_corresponding | False |

| authorships[3].raw_affiliation_strings | Univeristy of Trento, Italy |

| authorships[4].author.id | https://openalex.org/A5010135755 |

| authorships[4].author.orcid | https://orcid.org/0000-0001-8162-3792 |

| authorships[4].author.display_name | Nikolaos Alachiotis |

| authorships[4].countries | NL |

| authorships[4].affiliations[0].institution_ids | https://openalex.org/I94624287 |

| authorships[4].affiliations[0].raw_affiliation_string | University of Twente, The Netherlands |

| authorships[4].institutions[0].id | https://openalex.org/I94624287 |

| authorships[4].institutions[0].ror | https://ror.org/006hf6230 |

| authorships[4].institutions[0].type | education |

| authorships[4].institutions[0].lineage | https://openalex.org/I94624287 |

| authorships[4].institutions[0].country_code | NL |

| authorships[4].institutions[0].display_name | University of Twente |

| authorships[4].author_position | middle |

| authorships[4].raw_author_name | Nikolaos Alachiotis |

| authorships[4].is_corresponding | False |

| authorships[4].raw_affiliation_strings | University of Twente, The Netherlands |

| authorships[5].author.id | https://openalex.org/A5048232172 |

| authorships[5].author.orcid | https://orcid.org/0000-0002-5064-7342 |

| authorships[5].author.display_name | Marco Ottavi |

| authorships[5].countries | IT, NL |

| authorships[5].affiliations[0].institution_ids | https://openalex.org/I94624287 |

| authorships[5].affiliations[0].raw_affiliation_string | University of Twente, The Netherlands |

| authorships[5].affiliations[1].institution_ids | https://openalex.org/I116067653 |

| authorships[5].affiliations[1].raw_affiliation_string | University of Rome Tor Vergata, Italy |

| authorships[5].institutions[0].id | https://openalex.org/I116067653 |

| authorships[5].institutions[0].ror | https://ror.org/02p77k626 |

| authorships[5].institutions[0].type | education |

| authorships[5].institutions[0].lineage | https://openalex.org/I116067653 |

| authorships[5].institutions[0].country_code | IT |

| authorships[5].institutions[0].display_name | University of Rome Tor Vergata |

| authorships[5].institutions[1].id | https://openalex.org/I94624287 |

| authorships[5].institutions[1].ror | https://ror.org/006hf6230 |

| authorships[5].institutions[1].type | education |

| authorships[5].institutions[1].lineage | https://openalex.org/I94624287 |

| authorships[5].institutions[1].country_code | NL |

| authorships[5].institutions[1].display_name | University of Twente |

| authorships[5].author_position | last |

| authorships[5].raw_author_name | Marco Ottavi |

| authorships[5].is_corresponding | False |

| authorships[5].raw_affiliation_strings | University of Rome Tor Vergata, Italy, University of Twente, The Netherlands |

| has_content.pdf | False |

| has_content.grobid_xml | False |

| is_paratext | False |

| open_access.is_oa | True |

| open_access.oa_url | https://research.utwente.nl/en/publications/021d716d-f5e8-470b-9733-290911607378 |

| open_access.oa_status | gold |

| open_access.any_repository_has_fulltext | False |

| created_date | 2023-07-13T00:00:00 |

| display_name | An unprotected RISC-V Soft-core processor on an SRAM FPGA: Is it as bad as it sounds? |

| has_fulltext | False |

| is_retracted | False |

| updated_date | 2025-11-06T03:46:38.306776 |

| primary_topic.id | https://openalex.org/T11005 |

| primary_topic.field.id | https://openalex.org/fields/22 |

| primary_topic.field.display_name | Engineering |

| primary_topic.score | 1.0 |

| primary_topic.domain.id | https://openalex.org/domains/3 |

| primary_topic.domain.display_name | Physical Sciences |

| primary_topic.subfield.id | https://openalex.org/subfields/2208 |

| primary_topic.subfield.display_name | Electrical and Electronic Engineering |

| primary_topic.display_name | Radiation Effects in Electronics |

| related_works | https://openalex.org/W1544665014, https://openalex.org/W2748364266, https://openalex.org/W4243861219, https://openalex.org/W2556374054, https://openalex.org/W2069545207, https://openalex.org/W2092579166, https://openalex.org/W2969723039, https://openalex.org/W1977947048, https://openalex.org/W2914540329, https://openalex.org/W2906337187 |

| cited_by_count | 3 |

| counts_by_year[0].year | 2025 |

| counts_by_year[0].cited_by_count | 2 |

| counts_by_year[1].year | 2024 |

| counts_by_year[1].cited_by_count | 1 |

| locations_count | 5 |

| best_oa_location.id | pmh:oai:ris.utwente.nl:openaire_cris_publications/021d716d-f5e8-470b-9733-290911607378 |

| best_oa_location.is_oa | True |

| best_oa_location.source | |

| best_oa_location.license | other-oa |

| best_oa_location.pdf_url | |

| best_oa_location.version | submittedVersion |

| best_oa_location.raw_type | contributionToPeriodical |

| best_oa_location.license_id | https://openalex.org/licenses/other-oa |

| best_oa_location.is_accepted | False |

| best_oa_location.is_published | False |

| best_oa_location.raw_source_name | Forlin , B E , van Huffelen , W , Cazzaniga , C , Rech , P , Alachiotis , N & Ottavi , M 2023 , An unprotected RISC-V Soft-core processor on an SRAM FPGA : Is it as bad as it sounds? in Proceedings - 2023 IEEE European Test Symposium, ETS 2023 . Proceedings IEEE European Test Symposium (ETS) , vol. 2023 , IEEE , Piscataway, NJ , 28th IEEE European Test Symposium, ETS 2023 , Venice , Italy , 22/05/23 . https://doi.org/10.1109/ETS56758.2023.10174076 |

| best_oa_location.landing_page_url | https://research.utwente.nl/en/publications/021d716d-f5e8-470b-9733-290911607378 |

| primary_location.id | doi:10.1109/ets56758.2023.10174076 |

| primary_location.is_oa | False |

| primary_location.source | |

| primary_location.license | |

| primary_location.pdf_url | |

| primary_location.version | publishedVersion |

| primary_location.raw_type | proceedings-article |

| primary_location.license_id | |

| primary_location.is_accepted | True |

| primary_location.is_published | True |

| primary_location.raw_source_name | 2023 IEEE European Test Symposium (ETS) |

| primary_location.landing_page_url | https://doi.org/10.1109/ets56758.2023.10174076 |

| publication_date | 2023-05-22 |

| publication_year | 2023 |

| referenced_works | https://openalex.org/W2806892359, https://openalex.org/W2123907700, https://openalex.org/W3197721294, https://openalex.org/W6697572560, https://openalex.org/W2771049336, https://openalex.org/W2806983213, https://openalex.org/W3046320443, https://openalex.org/W4280566890, https://openalex.org/W3115144728, https://openalex.org/W2978231018, https://openalex.org/W3146456515, https://openalex.org/W2559705978, https://openalex.org/W2559930489, https://openalex.org/W2944339534, https://openalex.org/W3026432130, https://openalex.org/W4283119709, https://openalex.org/W2529578574, https://openalex.org/W4297336601, https://openalex.org/W2296343188, https://openalex.org/W2369855514 |

| referenced_works_count | 20 |

| abstract_inverted_index.a | 49 |

| abstract_inverted_index.By | 112 |

| abstract_inverted_index.We | 68 |

| abstract_inverted_index.an | 73, 78 |

| abstract_inverted_index.be | 38 |

| abstract_inverted_index.in | 24, 95, 109 |

| abstract_inverted_index.is | 56, 99 |

| abstract_inverted_index.it | 55 |

| abstract_inverted_index.of | 40, 72, 103, 107, 123, 131 |

| abstract_inverted_index.on | 28 |

| abstract_inverted_index.or | 145 |

| abstract_inverted_index.to | 22, 58, 64 |

| abstract_inverted_index.we | 117 |

| abstract_inverted_index.For | 32 |

| abstract_inverted_index.Our | 82 |

| abstract_inverted_index.and | 4, 27, 90, 127 |

| abstract_inverted_index.are | 6, 20, 62 |

| abstract_inverted_index.for | 10, 52, 86 |

| abstract_inverted_index.low | 2 |

| abstract_inverted_index.our | 87 |

| abstract_inverted_index.the | 25, 29, 70, 92, 96, 100, 104, 110, 114, 121, 124, 132, 137 |

| abstract_inverted_index.Fast | 0 |

| abstract_inverted_index.SRAM | 14, 18 |

| abstract_inverted_index.When | 47 |

| abstract_inverted_index.core | 51 |

| abstract_inverted_index.data | 94, 133, 144, 148 |

| abstract_inverted_index.from | 140, 146 |

| abstract_inverted_index.know | 59 |

| abstract_inverted_index.most | 130 |

| abstract_inverted_index.much | 45 |

| abstract_inverted_index.must | 37 |

| abstract_inverted_index.root | 119 |

| abstract_inverted_index.runs | 138 |

| abstract_inverted_index.soft | 50 |

| abstract_inverted_index.stem | 139 |

| abstract_inverted_index.that | 129, 149 |

| abstract_inverted_index.they | 36 |

| abstract_inverted_index.user | 26, 93 |

| abstract_inverted_index.were | 150 |

| abstract_inverted_index.FPGAs | 15, 19 |

| abstract_inverted_index.avoid | 65 |

| abstract_inverted_index.banks | 98 |

| abstract_inverted_index.beam. | 81 |

| abstract_inverted_index.bits. | 31 |

| abstract_inverted_index.cause | 102, 120 |

| abstract_inverted_index.cost, | 3 |

| abstract_inverted_index.could | 118 |

| abstract_inverted_index.found | 128 |

| abstract_inverted_index.input | 143 |

| abstract_inverted_index.prone | 21 |

| abstract_inverted_index.shows | 84 |

| abstract_inverted_index.that, | 85 |

| abstract_inverted_index.their | 33 |

| abstract_inverted_index.these | 53 |

| abstract_inverted_index.total | 105 |

| abstract_inverted_index.using | 77 |

| abstract_inverted_index.where | 60 |

| abstract_inverted_index.while | 152 |

| abstract_inverted_index.RISC-V | 75 |

| abstract_inverted_index.chosen | 88 |

| abstract_inverted_index.during | 136 |

| abstract_inverted_index.errors | 23, 108, 126 |

| abstract_inverted_index.making | 13 |

| abstract_inverted_index.memory | 97 |

| abstract_inverted_index.number | 106 |

| abstract_inverted_index.origin | 122 |

| abstract_inverted_index.output | 147 |

| abstract_inverted_index.capable | 39 |

| abstract_inverted_index.correct | 34 |

| abstract_inverted_index.corrupt | 142 |

| abstract_inverted_index.factors | 9 |

| abstract_inverted_index.leading | 101 |

| abstract_inverted_index.neutron | 80 |

| abstract_inverted_index.without | 43 |

| abstract_inverted_index.However, | 17 |

| abstract_inverted_index.becoming | 7 |

| abstract_inverted_index.critical | 8 |

| abstract_inverted_index.detected | 135 |

| abstract_inverted_index.failures | 42 |

| abstract_inverted_index.observed | 125 |

| abstract_inverted_index.adjusting | 48 |

| abstract_inverted_index.aerospace | 11 |

| abstract_inverted_index.benchmark | 89, 115 |

| abstract_inverted_index.corrupted | 151 |

| abstract_inverted_index.essential | 57 |

| abstract_inverted_index.overhead. | 67 |

| abstract_inverted_index.reversing | 113 |

| abstract_inverted_index.corruption | 134 |

| abstract_inverted_index.necessary, | 63 |

| abstract_inverted_index.previously | 141 |

| abstract_inverted_index.processor, | 91 |

| abstract_inverted_index.accelerated | 79 |

| abstract_inverted_index.attractive. | 16 |

| abstract_inverted_index.operations, | 116 |

| abstract_inverted_index.reliability | 71 |

| abstract_inverted_index.sacrificing | 44 |

| abstract_inverted_index.unnecessary | 66 |

| abstract_inverted_index.unprotected | 74 |

| abstract_inverted_index.application. | 111 |

| abstract_inverted_index.characterize | 69 |

| abstract_inverted_index.development, | 1 |

| abstract_inverted_index.functioning, | 35 |

| abstract_inverted_index.performance. | 46 |

| abstract_inverted_index.redundancies | 61 |

| abstract_inverted_index.withstanding | 41 |

| abstract_inverted_index.applications, | 12, 54 |

| abstract_inverted_index.configuration | 30 |

| abstract_inverted_index.investigation | 83 |

| abstract_inverted_index.transmitting. | 153 |

| abstract_inverted_index.microcontroller | 76 |

| abstract_inverted_index.reconfigurability | 5 |

| cited_by_percentile_year.max | 97 |

| cited_by_percentile_year.min | 90 |

| countries_distinct_count | 3 |

| institutions_distinct_count | 6 |

| sustainable_development_goals[0].id | https://metadata.un.org/sdg/16 |

| sustainable_development_goals[0].score | 0.8199999928474426 |

| sustainable_development_goals[0].display_name | Peace, Justice and strong institutions |

| citation_normalized_percentile.value | 0.62935682 |

| citation_normalized_percentile.is_in_top_1_percent | False |

| citation_normalized_percentile.is_in_top_10_percent | False |