FPGA Implementation of Fault Tolerant Full Adder Design for High Speed VLSI Architectures Article Swipe

Vikas Maheshwari

,

R. S. Singh

·

YOU?

·

· 2019

· Open Access

·

· DOI: https://doi.org/10.35940/ijrte.b1248.0782s319

YOU?

·

· 2019

· Open Access

·

· DOI: https://doi.org/10.35940/ijrte.b1248.0782s319

YOU?

·

· 2019

· Open Access

·

· DOI: https://doi.org/10.35940/ijrte.b1248.0782s319

YOU?

·

· 2019

· Open Access

·

· DOI: https://doi.org/10.35940/ijrte.b1248.0782s319

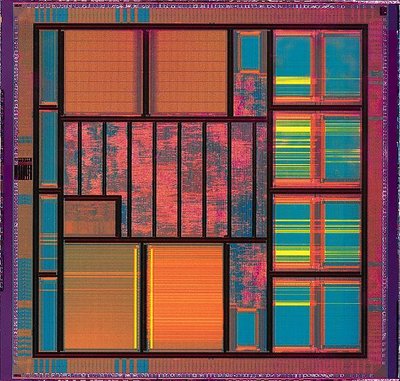

The essential goal is to distinguish and diminish the deficiencies in full Adder configuration making use of Self checking and Self Repairing Adder Block. The tempo of chip disappointment is straightforwardly relative to chip thickness. A framework should be flaw tolerant to diminish the frustration rate. The nearness of different troubles can demolish the usefulness of complete snake. This paper displays a region proficient flaw tolerant complete snake shape that may repair issues without interfering with the everyday assignment of a framework. The combo and duplicate is finished through way of making use of Xilinx ISE 14.7 and actualized on FPGA Spartan three..

Related Topics

Concepts

Adder

Field-programmable gate array

Disappointment

Computer science

Block (permutation group theory)

Very-large-scale integration

Computer architecture

Chip

Parallel computing

Arithmetic

Fault tolerance

Spartan

Embedded system

Computer hardware

Mathematics

Psychology

Distributed computing

Telecommunications

Latency (audio)

Social psychology

Geometry

Metadata

- Type

- article

- Language

- en

- Landing Page

- https://doi.org/10.35940/ijrte.b1248.0782s319

- https://doi.org/10.35940/ijrte.b1248.0782s319

- OA Status

- diamond

- References

- 2

- Related Works

- 10

- OpenAlex ID

- https://openalex.org/W4237108225

All OpenAlex metadata

Raw OpenAlex JSON

- OpenAlex ID

-

https://openalex.org/W4237108225Canonical identifier for this work in OpenAlex

- DOI

-

https://doi.org/10.35940/ijrte.b1248.0782s319Digital Object Identifier

- Title

-

FPGA Implementation of Fault Tolerant Full Adder Design for High Speed VLSI ArchitecturesWork title

- Type

-

articleOpenAlex work type

- Language

-

enPrimary language

- Publication year

-

2019Year of publication

- Publication date

-

2019-08-10Full publication date if available

- Authors

-

Vikas Maheshwari, R. S. SinghList of authors in order

- Landing page

-

https://doi.org/10.35940/ijrte.b1248.0782s319Publisher landing page

- PDF URL

-

https://doi.org/10.35940/ijrte.b1248.0782s319Direct link to full text PDF

- Open access

-

YesWhether a free full text is available

- OA status

-

diamondOpen access status per OpenAlex

- OA URL

-

https://doi.org/10.35940/ijrte.b1248.0782s319Direct OA link when available

- Concepts

-

Adder, Field-programmable gate array, Disappointment, Computer science, Block (permutation group theory), Very-large-scale integration, Computer architecture, Chip, Parallel computing, Arithmetic, Fault tolerance, Spartan, Embedded system, Computer hardware, Mathematics, Psychology, Distributed computing, Telecommunications, Latency (audio), Social psychology, GeometryTop concepts (fields/topics) attached by OpenAlex

- Cited by

-

0Total citation count in OpenAlex

- References (count)

-

2Number of works referenced by this work

- Related works (count)

-

10Other works algorithmically related by OpenAlex

Full payload

| id | https://openalex.org/W4237108225 |

|---|---|

| doi | https://doi.org/10.35940/ijrte.b1248.0782s319 |

| ids.doi | https://doi.org/10.35940/ijrte.b1248.0782s319 |

| ids.openalex | https://openalex.org/W4237108225 |

| fwci | 0.0 |

| type | article |

| title | FPGA Implementation of Fault Tolerant Full Adder Design for High Speed VLSI Architectures |

| biblio.issue | 2S3 |

| biblio.volume | 8 |

| biblio.last_page | 1329 |

| biblio.first_page | 1325 |

| topics[0].id | https://openalex.org/T10558 |

| topics[0].field.id | https://openalex.org/fields/22 |

| topics[0].field.display_name | Engineering |

| topics[0].score | 0.9947999715805054 |

| topics[0].domain.id | https://openalex.org/domains/3 |

| topics[0].domain.display_name | Physical Sciences |

| topics[0].subfield.id | https://openalex.org/subfields/2208 |

| topics[0].subfield.display_name | Electrical and Electronic Engineering |

| topics[0].display_name | Advancements in Semiconductor Devices and Circuit Design |

| topics[1].id | https://openalex.org/T11032 |

| topics[1].field.id | https://openalex.org/fields/17 |

| topics[1].field.display_name | Computer Science |

| topics[1].score | 0.9922000169754028 |

| topics[1].domain.id | https://openalex.org/domains/3 |

| topics[1].domain.display_name | Physical Sciences |

| topics[1].subfield.id | https://openalex.org/subfields/1708 |

| topics[1].subfield.display_name | Hardware and Architecture |

| topics[1].display_name | VLSI and Analog Circuit Testing |

| topics[2].id | https://openalex.org/T10363 |

| topics[2].field.id | https://openalex.org/fields/22 |

| topics[2].field.display_name | Engineering |

| topics[2].score | 0.9915000200271606 |

| topics[2].domain.id | https://openalex.org/domains/3 |

| topics[2].domain.display_name | Physical Sciences |

| topics[2].subfield.id | https://openalex.org/subfields/2208 |

| topics[2].subfield.display_name | Electrical and Electronic Engineering |

| topics[2].display_name | Low-power high-performance VLSI design |

| is_xpac | False |

| apc_list | |

| apc_paid | |

| concepts[0].id | https://openalex.org/C164620267 |

| concepts[0].level | 3 |

| concepts[0].score | 0.944444477558136 |

| concepts[0].wikidata | https://www.wikidata.org/wiki/Q376953 |

| concepts[0].display_name | Adder |

| concepts[1].id | https://openalex.org/C42935608 |

| concepts[1].level | 2 |

| concepts[1].score | 0.7505286335945129 |

| concepts[1].wikidata | https://www.wikidata.org/wiki/Q190411 |

| concepts[1].display_name | Field-programmable gate array |

| concepts[2].id | https://openalex.org/C2779628136 |

| concepts[2].level | 2 |

| concepts[2].score | 0.6980888843536377 |

| concepts[2].wikidata | https://www.wikidata.org/wiki/Q621206 |

| concepts[2].display_name | Disappointment |

| concepts[3].id | https://openalex.org/C41008148 |

| concepts[3].level | 0 |

| concepts[3].score | 0.6513186693191528 |

| concepts[3].wikidata | https://www.wikidata.org/wiki/Q21198 |

| concepts[3].display_name | Computer science |

| concepts[4].id | https://openalex.org/C2777210771 |

| concepts[4].level | 2 |

| concepts[4].score | 0.5761793851852417 |

| concepts[4].wikidata | https://www.wikidata.org/wiki/Q4927124 |

| concepts[4].display_name | Block (permutation group theory) |

| concepts[5].id | https://openalex.org/C14580979 |

| concepts[5].level | 2 |

| concepts[5].score | 0.5569234490394592 |

| concepts[5].wikidata | https://www.wikidata.org/wiki/Q876049 |

| concepts[5].display_name | Very-large-scale integration |

| concepts[6].id | https://openalex.org/C118524514 |

| concepts[6].level | 1 |

| concepts[6].score | 0.5202337503433228 |

| concepts[6].wikidata | https://www.wikidata.org/wiki/Q173212 |

| concepts[6].display_name | Computer architecture |

| concepts[7].id | https://openalex.org/C165005293 |

| concepts[7].level | 2 |

| concepts[7].score | 0.49749234318733215 |

| concepts[7].wikidata | https://www.wikidata.org/wiki/Q1074500 |

| concepts[7].display_name | Chip |

| concepts[8].id | https://openalex.org/C173608175 |

| concepts[8].level | 1 |

| concepts[8].score | 0.43121084570884705 |

| concepts[8].wikidata | https://www.wikidata.org/wiki/Q232661 |

| concepts[8].display_name | Parallel computing |

| concepts[9].id | https://openalex.org/C94375191 |

| concepts[9].level | 1 |

| concepts[9].score | 0.4279424846172333 |

| concepts[9].wikidata | https://www.wikidata.org/wiki/Q11205 |

| concepts[9].display_name | Arithmetic |

| concepts[10].id | https://openalex.org/C63540848 |

| concepts[10].level | 2 |

| concepts[10].score | 0.4204915165901184 |

| concepts[10].wikidata | https://www.wikidata.org/wiki/Q3140932 |

| concepts[10].display_name | Fault tolerance |

| concepts[11].id | https://openalex.org/C10689553 |

| concepts[11].level | 3 |

| concepts[11].score | 0.41869133710861206 |

| concepts[11].wikidata | https://www.wikidata.org/wiki/Q405953 |

| concepts[11].display_name | Spartan |

| concepts[12].id | https://openalex.org/C149635348 |

| concepts[12].level | 1 |

| concepts[12].score | 0.40625154972076416 |

| concepts[12].wikidata | https://www.wikidata.org/wiki/Q193040 |

| concepts[12].display_name | Embedded system |

| concepts[13].id | https://openalex.org/C9390403 |

| concepts[13].level | 1 |

| concepts[13].score | 0.3731117844581604 |

| concepts[13].wikidata | https://www.wikidata.org/wiki/Q3966 |

| concepts[13].display_name | Computer hardware |

| concepts[14].id | https://openalex.org/C33923547 |

| concepts[14].level | 0 |

| concepts[14].score | 0.10647055506706238 |

| concepts[14].wikidata | https://www.wikidata.org/wiki/Q395 |

| concepts[14].display_name | Mathematics |

| concepts[15].id | https://openalex.org/C15744967 |

| concepts[15].level | 0 |

| concepts[15].score | 0.10526585578918457 |

| concepts[15].wikidata | https://www.wikidata.org/wiki/Q9418 |

| concepts[15].display_name | Psychology |

| concepts[16].id | https://openalex.org/C120314980 |

| concepts[16].level | 1 |

| concepts[16].score | 0.10345694422721863 |

| concepts[16].wikidata | https://www.wikidata.org/wiki/Q180634 |

| concepts[16].display_name | Distributed computing |

| concepts[17].id | https://openalex.org/C76155785 |

| concepts[17].level | 1 |

| concepts[17].score | 0.07596233487129211 |

| concepts[17].wikidata | https://www.wikidata.org/wiki/Q418 |

| concepts[17].display_name | Telecommunications |

| concepts[18].id | https://openalex.org/C82876162 |

| concepts[18].level | 2 |

| concepts[18].score | 0.0 |

| concepts[18].wikidata | https://www.wikidata.org/wiki/Q17096504 |

| concepts[18].display_name | Latency (audio) |

| concepts[19].id | https://openalex.org/C77805123 |

| concepts[19].level | 1 |

| concepts[19].score | 0.0 |

| concepts[19].wikidata | https://www.wikidata.org/wiki/Q161272 |

| concepts[19].display_name | Social psychology |

| concepts[20].id | https://openalex.org/C2524010 |

| concepts[20].level | 1 |

| concepts[20].score | 0.0 |

| concepts[20].wikidata | https://www.wikidata.org/wiki/Q8087 |

| concepts[20].display_name | Geometry |

| keywords[0].id | https://openalex.org/keywords/adder |

| keywords[0].score | 0.944444477558136 |

| keywords[0].display_name | Adder |

| keywords[1].id | https://openalex.org/keywords/field-programmable-gate-array |

| keywords[1].score | 0.7505286335945129 |

| keywords[1].display_name | Field-programmable gate array |

| keywords[2].id | https://openalex.org/keywords/disappointment |

| keywords[2].score | 0.6980888843536377 |

| keywords[2].display_name | Disappointment |

| keywords[3].id | https://openalex.org/keywords/computer-science |

| keywords[3].score | 0.6513186693191528 |

| keywords[3].display_name | Computer science |

| keywords[4].id | https://openalex.org/keywords/block |

| keywords[4].score | 0.5761793851852417 |

| keywords[4].display_name | Block (permutation group theory) |

| keywords[5].id | https://openalex.org/keywords/very-large-scale-integration |

| keywords[5].score | 0.5569234490394592 |

| keywords[5].display_name | Very-large-scale integration |

| keywords[6].id | https://openalex.org/keywords/computer-architecture |

| keywords[6].score | 0.5202337503433228 |

| keywords[6].display_name | Computer architecture |

| keywords[7].id | https://openalex.org/keywords/chip |

| keywords[7].score | 0.49749234318733215 |

| keywords[7].display_name | Chip |

| keywords[8].id | https://openalex.org/keywords/parallel-computing |

| keywords[8].score | 0.43121084570884705 |

| keywords[8].display_name | Parallel computing |

| keywords[9].id | https://openalex.org/keywords/arithmetic |

| keywords[9].score | 0.4279424846172333 |

| keywords[9].display_name | Arithmetic |

| keywords[10].id | https://openalex.org/keywords/fault-tolerance |

| keywords[10].score | 0.4204915165901184 |

| keywords[10].display_name | Fault tolerance |

| keywords[11].id | https://openalex.org/keywords/spartan |

| keywords[11].score | 0.41869133710861206 |

| keywords[11].display_name | Spartan |

| keywords[12].id | https://openalex.org/keywords/embedded-system |

| keywords[12].score | 0.40625154972076416 |

| keywords[12].display_name | Embedded system |

| keywords[13].id | https://openalex.org/keywords/computer-hardware |

| keywords[13].score | 0.3731117844581604 |

| keywords[13].display_name | Computer hardware |

| keywords[14].id | https://openalex.org/keywords/mathematics |

| keywords[14].score | 0.10647055506706238 |

| keywords[14].display_name | Mathematics |

| keywords[15].id | https://openalex.org/keywords/psychology |

| keywords[15].score | 0.10526585578918457 |

| keywords[15].display_name | Psychology |

| keywords[16].id | https://openalex.org/keywords/distributed-computing |

| keywords[16].score | 0.10345694422721863 |

| keywords[16].display_name | Distributed computing |

| keywords[17].id | https://openalex.org/keywords/telecommunications |

| keywords[17].score | 0.07596233487129211 |

| keywords[17].display_name | Telecommunications |

| language | en |

| locations[0].id | doi:10.35940/ijrte.b1248.0782s319 |

| locations[0].is_oa | True |

| locations[0].source.id | https://openalex.org/S4210169567 |

| locations[0].source.issn | 2277-3878 |

| locations[0].source.type | journal |

| locations[0].source.is_oa | True |

| locations[0].source.issn_l | 2277-3878 |

| locations[0].source.is_core | True |

| locations[0].source.is_in_doaj | False |

| locations[0].source.display_name | International Journal of Recent Technology and Engineering (IJRTE) |

| locations[0].source.host_organization | |

| locations[0].source.host_organization_name | |

| locations[0].license | |

| locations[0].pdf_url | https://doi.org/10.35940/ijrte.b1248.0782s319 |

| locations[0].version | publishedVersion |

| locations[0].raw_type | journal-article |

| locations[0].license_id | |

| locations[0].is_accepted | True |

| locations[0].is_published | True |

| locations[0].raw_source_name | International Journal of Recent Technology and Engineering |

| locations[0].landing_page_url | https://doi.org/10.35940/ijrte.b1248.0782s319 |

| indexed_in | crossref |

| authorships[0].author.id | https://openalex.org/A5026531367 |

| authorships[0].author.orcid | https://orcid.org/0000-0002-4106-9034 |

| authorships[0].author.display_name | Vikas Maheshwari |

| authorships[0].countries | IN |

| authorships[0].affiliations[0].institution_ids | https://openalex.org/I134892692 |

| authorships[0].affiliations[0].raw_affiliation_string | Dept. of ECE, Bharat Institute of Engineering and Technology, Hyderabad. India. |

| authorships[0].institutions[0].id | https://openalex.org/I134892692 |

| authorships[0].institutions[0].ror | https://ror.org/047ymzq84 |

| authorships[0].institutions[0].type | education |

| authorships[0].institutions[0].lineage | https://openalex.org/I134892692 |

| authorships[0].institutions[0].country_code | IN |

| authorships[0].institutions[0].display_name | Chaitanya Bharathi Institute of Technology |

| authorships[0].author_position | first |

| authorships[0].raw_author_name | Vikas Maheshwari |

| authorships[0].is_corresponding | False |

| authorships[0].raw_affiliation_strings | Dept. of ECE, Bharat Institute of Engineering and Technology, Hyderabad. India. |

| authorships[1].author.id | https://openalex.org/A5053636373 |

| authorships[1].author.orcid | https://orcid.org/0000-0003-3268-7057 |

| authorships[1].author.display_name | R. S. Singh |

| authorships[1].countries | IN |

| authorships[1].affiliations[0].institution_ids | https://openalex.org/I134892692 |

| authorships[1].affiliations[0].raw_affiliation_string | Dept. of ECE, Bharat Institute of Engineering and Technology, Hyderabad. India. |

| authorships[1].institutions[0].id | https://openalex.org/I134892692 |

| authorships[1].institutions[0].ror | https://ror.org/047ymzq84 |

| authorships[1].institutions[0].type | education |

| authorships[1].institutions[0].lineage | https://openalex.org/I134892692 |

| authorships[1].institutions[0].country_code | IN |

| authorships[1].institutions[0].display_name | Chaitanya Bharathi Institute of Technology |

| authorships[1].author_position | last |

| authorships[1].raw_author_name | R Singh |

| authorships[1].is_corresponding | False |

| authorships[1].raw_affiliation_strings | Dept. of ECE, Bharat Institute of Engineering and Technology, Hyderabad. India. |

| has_content.pdf | True |

| has_content.grobid_xml | True |

| is_paratext | False |

| open_access.is_oa | True |

| open_access.oa_url | https://doi.org/10.35940/ijrte.b1248.0782s319 |

| open_access.oa_status | diamond |

| open_access.any_repository_has_fulltext | False |

| created_date | 2022-05-12T00:00:00 |

| display_name | FPGA Implementation of Fault Tolerant Full Adder Design for High Speed VLSI Architectures |

| has_fulltext | True |

| is_retracted | False |

| updated_date | 2025-11-06T03:46:38.306776 |

| primary_topic.id | https://openalex.org/T10558 |

| primary_topic.field.id | https://openalex.org/fields/22 |

| primary_topic.field.display_name | Engineering |

| primary_topic.score | 0.9947999715805054 |

| primary_topic.domain.id | https://openalex.org/domains/3 |

| primary_topic.domain.display_name | Physical Sciences |

| primary_topic.subfield.id | https://openalex.org/subfields/2208 |

| primary_topic.subfield.display_name | Electrical and Electronic Engineering |

| primary_topic.display_name | Advancements in Semiconductor Devices and Circuit Design |

| related_works | https://openalex.org/W2980006224, https://openalex.org/W2218697068, https://openalex.org/W4311227653, https://openalex.org/W2171847407, https://openalex.org/W4308216800, https://openalex.org/W2571254419, https://openalex.org/W2363310833, https://openalex.org/W2372009607, https://openalex.org/W4205810114, https://openalex.org/W2349074811 |

| cited_by_count | 0 |

| locations_count | 1 |

| best_oa_location.id | doi:10.35940/ijrte.b1248.0782s319 |

| best_oa_location.is_oa | True |

| best_oa_location.source.id | https://openalex.org/S4210169567 |

| best_oa_location.source.issn | 2277-3878 |

| best_oa_location.source.type | journal |

| best_oa_location.source.is_oa | True |

| best_oa_location.source.issn_l | 2277-3878 |

| best_oa_location.source.is_core | True |

| best_oa_location.source.is_in_doaj | False |

| best_oa_location.source.display_name | International Journal of Recent Technology and Engineering (IJRTE) |

| best_oa_location.source.host_organization | |

| best_oa_location.source.host_organization_name | |

| best_oa_location.license | |

| best_oa_location.pdf_url | https://doi.org/10.35940/ijrte.b1248.0782s319 |

| best_oa_location.version | publishedVersion |

| best_oa_location.raw_type | journal-article |

| best_oa_location.license_id | |

| best_oa_location.is_accepted | True |

| best_oa_location.is_published | True |

| best_oa_location.raw_source_name | International Journal of Recent Technology and Engineering |

| best_oa_location.landing_page_url | https://doi.org/10.35940/ijrte.b1248.0782s319 |

| primary_location.id | doi:10.35940/ijrte.b1248.0782s319 |

| primary_location.is_oa | True |

| primary_location.source.id | https://openalex.org/S4210169567 |

| primary_location.source.issn | 2277-3878 |

| primary_location.source.type | journal |

| primary_location.source.is_oa | True |

| primary_location.source.issn_l | 2277-3878 |

| primary_location.source.is_core | True |

| primary_location.source.is_in_doaj | False |

| primary_location.source.display_name | International Journal of Recent Technology and Engineering (IJRTE) |

| primary_location.source.host_organization | |

| primary_location.source.host_organization_name | |

| primary_location.license | |

| primary_location.pdf_url | https://doi.org/10.35940/ijrte.b1248.0782s319 |

| primary_location.version | publishedVersion |

| primary_location.raw_type | journal-article |

| primary_location.license_id | |

| primary_location.is_accepted | True |

| primary_location.is_published | True |

| primary_location.raw_source_name | International Journal of Recent Technology and Engineering |

| primary_location.landing_page_url | https://doi.org/10.35940/ijrte.b1248.0782s319 |

| publication_date | 2019-08-10 |

| publication_year | 2019 |

| referenced_works | https://openalex.org/W1985989665, https://openalex.org/W2902593524 |

| referenced_works_count | 2 |

| abstract_inverted_index.A | 35 |

| abstract_inverted_index.a | 61, 80 |

| abstract_inverted_index.be | 38 |

| abstract_inverted_index.in | 10 |

| abstract_inverted_index.is | 3, 29, 86 |

| abstract_inverted_index.of | 16, 26, 48, 55, 79, 90, 93 |

| abstract_inverted_index.on | 99 |

| abstract_inverted_index.to | 4, 32, 41 |

| abstract_inverted_index.ISE | 95 |

| abstract_inverted_index.The | 0, 24, 46, 82 |

| abstract_inverted_index.and | 6, 19, 84, 97 |

| abstract_inverted_index.can | 51 |

| abstract_inverted_index.may | 70 |

| abstract_inverted_index.the | 8, 43, 53, 76 |

| abstract_inverted_index.use | 15, 92 |

| abstract_inverted_index.way | 89 |

| abstract_inverted_index.14.7 | 96 |

| abstract_inverted_index.FPGA | 100 |

| abstract_inverted_index.Self | 17, 20 |

| abstract_inverted_index.This | 58 |

| abstract_inverted_index.chip | 27, 33 |

| abstract_inverted_index.flaw | 39, 64 |

| abstract_inverted_index.full | 11 |

| abstract_inverted_index.goal | 2 |

| abstract_inverted_index.that | 69 |

| abstract_inverted_index.with | 75 |

| abstract_inverted_index.Adder | 12, 22 |

| abstract_inverted_index.combo | 83 |

| abstract_inverted_index.paper | 59 |

| abstract_inverted_index.rate. | 45 |

| abstract_inverted_index.shape | 68 |

| abstract_inverted_index.snake | 67 |

| abstract_inverted_index.tempo | 25 |

| abstract_inverted_index.Block. | 23 |

| abstract_inverted_index.Xilinx | 94 |

| abstract_inverted_index.issues | 72 |

| abstract_inverted_index.making | 14, 91 |

| abstract_inverted_index.region | 62 |

| abstract_inverted_index.repair | 71 |

| abstract_inverted_index.should | 37 |

| abstract_inverted_index.snake. | 57 |

| abstract_inverted_index.Spartan | 101 |

| abstract_inverted_index.three.. | 102 |

| abstract_inverted_index.through | 88 |

| abstract_inverted_index.without | 73 |

| abstract_inverted_index.checking | 18 |

| abstract_inverted_index.complete | 56, 66 |

| abstract_inverted_index.demolish | 52 |

| abstract_inverted_index.diminish | 7, 42 |

| abstract_inverted_index.displays | 60 |

| abstract_inverted_index.everyday | 77 |

| abstract_inverted_index.finished | 87 |

| abstract_inverted_index.nearness | 47 |

| abstract_inverted_index.relative | 31 |

| abstract_inverted_index.tolerant | 40, 65 |

| abstract_inverted_index.troubles | 50 |

| abstract_inverted_index.Repairing | 21 |

| abstract_inverted_index.different | 49 |

| abstract_inverted_index.duplicate | 85 |

| abstract_inverted_index.essential | 1 |

| abstract_inverted_index.framework | 36 |

| abstract_inverted_index.actualized | 98 |

| abstract_inverted_index.assignment | 78 |

| abstract_inverted_index.framework. | 81 |

| abstract_inverted_index.proficient | 63 |

| abstract_inverted_index.thickness. | 34 |

| abstract_inverted_index.usefulness | 54 |

| abstract_inverted_index.distinguish | 5 |

| abstract_inverted_index.frustration | 44 |

| abstract_inverted_index.interfering | 74 |

| abstract_inverted_index.deficiencies | 9 |

| abstract_inverted_index.configuration | 13 |

| abstract_inverted_index.disappointment | 28 |

| abstract_inverted_index.straightforwardly | 30 |

| cited_by_percentile_year | |

| countries_distinct_count | 1 |

| institutions_distinct_count | 2 |

| citation_normalized_percentile.value | 0.24551794 |

| citation_normalized_percentile.is_in_top_1_percent | False |

| citation_normalized_percentile.is_in_top_10_percent | False |