FPGA implementation of integrated circuit interactions along with modem connectivity and adapter transponder Article Swipe

YOU?

·

· 2022

· Open Access

·

· DOI: https://doi.org/10.1063/5.0109796

YOU?

·

· 2022

· Open Access

·

· DOI: https://doi.org/10.1063/5.0109796

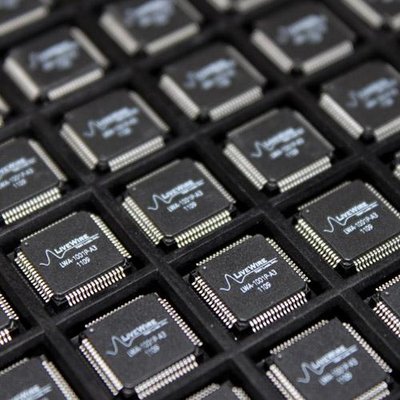

The process of transmitting data in field-programmable gate array via USB connected with serial interface engine and FIFO is presented in this paper. The SIE component transmits inputs to also be communicated from some kind of PC's centralized processor unit as well as passes so many through the standardized transmission conventional cellular interface, that takes care of many transmission-related concerns such as transmitting data but also rehabilitation.A 2Kb queue is prepared in assuring effective conversation between multiple FPGA processors.To convert input data of parallel form into output data of serial form, PISO converter is used. Device Information Notification is being used to make sure that the information is already in USB routing protocol. The data checking assertions are generally categorized as based on expected for cyclic consistency. The incoming signal is then transformed in to other electronic signals that use the SIPO component that once data has been analyzed.The FPGA-to-FPGA data transmission system is working properly.An implementation electronic device (example ASIC) is created utilizing Transistor.The number of gates are 14,547, consumption of power is 2.6742 mW and the frequency is 50MHz at a voltage and pin numbers of 1.8 V and 38 respectively.

Related Topics

- Type

- article

- Language

- en

- Landing Page

- https://doi.org/10.1063/5.0109796

- https://aip.scitation.org/doi/pdf/10.1063/5.0109796

- OA Status

- bronze

- Cited By

- 1

- References

- 16

- Related Works

- 10

- OpenAlex ID

- https://openalex.org/W4312751918

Raw OpenAlex JSON

- OpenAlex ID

-

https://openalex.org/W4312751918Canonical identifier for this work in OpenAlex

- DOI

-

https://doi.org/10.1063/5.0109796Digital Object Identifier

- Title

-

FPGA implementation of integrated circuit interactions along with modem connectivity and adapter transponderWork title

- Type

-

articleOpenAlex work type

- Language

-

enPrimary language

- Publication year

-

2022Year of publication

- Publication date

-

2022-01-01Full publication date if available

- Authors

-

S. Mahaboob Basha, A. Arun, T.D. Subha, V. Bhuvaneswari, D. Kalai Selvi, J. Nain SankarList of authors in order

- Landing page

-

https://doi.org/10.1063/5.0109796Publisher landing page

- PDF URL

-

https://aip.scitation.org/doi/pdf/10.1063/5.0109796Direct link to full text PDF

- Open access

-

YesWhether a free full text is available

- OA status

-

bronzeOpen access status per OpenAlex

- OA URL

-

https://aip.scitation.org/doi/pdf/10.1063/5.0109796Direct OA link when available

- Concepts

-

USB, Computer science, Embedded system, Computer hardware, Field-programmable gate array, Serial communication, Adapter (computing), Application-specific integrated circuit, Gate array, Interface (matter), Handshake, Asynchronous communication, Computer network, Operating system, Bubble, Maximum bubble pressure method, SoftwareTop concepts (fields/topics) attached by OpenAlex

- Cited by

-

1Total citation count in OpenAlex

- Citations by year (recent)

-

2023: 1Per-year citation counts (last 5 years)

- References (count)

-

16Number of works referenced by this work

- Related works (count)

-

10Other works algorithmically related by OpenAlex

Full payload

| id | https://openalex.org/W4312751918 |

|---|---|

| doi | https://doi.org/10.1063/5.0109796 |

| ids.doi | https://doi.org/10.1063/5.0109796 |

| ids.openalex | https://openalex.org/W4312751918 |

| fwci | 0.14927785 |

| type | article |

| title | FPGA implementation of integrated circuit interactions along with modem connectivity and adapter transponder |

| biblio.issue | |

| biblio.volume | 2676 |

| biblio.last_page | 050037 |

| biblio.first_page | 050037 |

| topics[0].id | https://openalex.org/T12941 |

| topics[0].field.id | https://openalex.org/fields/22 |

| topics[0].field.display_name | Engineering |

| topics[0].score | 0.9965000152587891 |

| topics[0].domain.id | https://openalex.org/domains/3 |

| topics[0].domain.display_name | Physical Sciences |

| topics[0].subfield.id | https://openalex.org/subfields/2207 |

| topics[0].subfield.display_name | Control and Systems Engineering |

| topics[0].display_name | Embedded Systems and FPGA Design |

| topics[1].id | https://openalex.org/T10904 |

| topics[1].field.id | https://openalex.org/fields/17 |

| topics[1].field.display_name | Computer Science |

| topics[1].score | 0.9950000047683716 |

| topics[1].domain.id | https://openalex.org/domains/3 |

| topics[1].domain.display_name | Physical Sciences |

| topics[1].subfield.id | https://openalex.org/subfields/1708 |

| topics[1].subfield.display_name | Hardware and Architecture |

| topics[1].display_name | Embedded Systems Design Techniques |

| topics[2].id | https://openalex.org/T13292 |

| topics[2].field.id | https://openalex.org/fields/22 |

| topics[2].field.display_name | Engineering |

| topics[2].score | 0.9944999814033508 |

| topics[2].domain.id | https://openalex.org/domains/3 |

| topics[2].domain.display_name | Physical Sciences |

| topics[2].subfield.id | https://openalex.org/subfields/2208 |

| topics[2].subfield.display_name | Electrical and Electronic Engineering |

| topics[2].display_name | Embedded Systems and FPGA Applications |

| is_xpac | False |

| apc_list | |

| apc_paid | |

| concepts[0].id | https://openalex.org/C507366226 |

| concepts[0].level | 3 |

| concepts[0].score | 0.7385517954826355 |

| concepts[0].wikidata | https://www.wikidata.org/wiki/Q42378 |

| concepts[0].display_name | USB |

| concepts[1].id | https://openalex.org/C41008148 |

| concepts[1].level | 0 |

| concepts[1].score | 0.7024036645889282 |

| concepts[1].wikidata | https://www.wikidata.org/wiki/Q21198 |

| concepts[1].display_name | Computer science |

| concepts[2].id | https://openalex.org/C149635348 |

| concepts[2].level | 1 |

| concepts[2].score | 0.6250280141830444 |

| concepts[2].wikidata | https://www.wikidata.org/wiki/Q193040 |

| concepts[2].display_name | Embedded system |

| concepts[3].id | https://openalex.org/C9390403 |

| concepts[3].level | 1 |

| concepts[3].score | 0.624546229839325 |

| concepts[3].wikidata | https://www.wikidata.org/wiki/Q3966 |

| concepts[3].display_name | Computer hardware |

| concepts[4].id | https://openalex.org/C42935608 |

| concepts[4].level | 2 |

| concepts[4].score | 0.5850247144699097 |

| concepts[4].wikidata | https://www.wikidata.org/wiki/Q190411 |

| concepts[4].display_name | Field-programmable gate array |

| concepts[5].id | https://openalex.org/C51707140 |

| concepts[5].level | 2 |

| concepts[5].score | 0.503497302532196 |

| concepts[5].wikidata | https://www.wikidata.org/wiki/Q518280 |

| concepts[5].display_name | Serial communication |

| concepts[6].id | https://openalex.org/C177284502 |

| concepts[6].level | 2 |

| concepts[6].score | 0.4968924820423126 |

| concepts[6].wikidata | https://www.wikidata.org/wiki/Q1005390 |

| concepts[6].display_name | Adapter (computing) |

| concepts[7].id | https://openalex.org/C77390884 |

| concepts[7].level | 2 |

| concepts[7].score | 0.4569379389286041 |

| concepts[7].wikidata | https://www.wikidata.org/wiki/Q217302 |

| concepts[7].display_name | Application-specific integrated circuit |

| concepts[8].id | https://openalex.org/C114237110 |

| concepts[8].level | 3 |

| concepts[8].score | 0.44805407524108887 |

| concepts[8].wikidata | https://www.wikidata.org/wiki/Q114901 |

| concepts[8].display_name | Gate array |

| concepts[9].id | https://openalex.org/C113843644 |

| concepts[9].level | 4 |

| concepts[9].score | 0.44588953256607056 |

| concepts[9].wikidata | https://www.wikidata.org/wiki/Q901882 |

| concepts[9].display_name | Interface (matter) |

| concepts[10].id | https://openalex.org/C2778000800 |

| concepts[10].level | 3 |

| concepts[10].score | 0.41299179196357727 |

| concepts[10].wikidata | https://www.wikidata.org/wiki/Q830043 |

| concepts[10].display_name | Handshake |

| concepts[11].id | https://openalex.org/C151319957 |

| concepts[11].level | 2 |

| concepts[11].score | 0.4104264974594116 |

| concepts[11].wikidata | https://www.wikidata.org/wiki/Q752739 |

| concepts[11].display_name | Asynchronous communication |

| concepts[12].id | https://openalex.org/C31258907 |

| concepts[12].level | 1 |

| concepts[12].score | 0.316172331571579 |

| concepts[12].wikidata | https://www.wikidata.org/wiki/Q1301371 |

| concepts[12].display_name | Computer network |

| concepts[13].id | https://openalex.org/C111919701 |

| concepts[13].level | 1 |

| concepts[13].score | 0.12389713525772095 |

| concepts[13].wikidata | https://www.wikidata.org/wiki/Q9135 |

| concepts[13].display_name | Operating system |

| concepts[14].id | https://openalex.org/C157915830 |

| concepts[14].level | 2 |

| concepts[14].score | 0.0 |

| concepts[14].wikidata | https://www.wikidata.org/wiki/Q2928001 |

| concepts[14].display_name | Bubble |

| concepts[15].id | https://openalex.org/C129307140 |

| concepts[15].level | 3 |

| concepts[15].score | 0.0 |

| concepts[15].wikidata | https://www.wikidata.org/wiki/Q6795880 |

| concepts[15].display_name | Maximum bubble pressure method |

| concepts[16].id | https://openalex.org/C2777904410 |

| concepts[16].level | 2 |

| concepts[16].score | 0.0 |

| concepts[16].wikidata | https://www.wikidata.org/wiki/Q7397 |

| concepts[16].display_name | Software |

| keywords[0].id | https://openalex.org/keywords/usb |

| keywords[0].score | 0.7385517954826355 |

| keywords[0].display_name | USB |

| keywords[1].id | https://openalex.org/keywords/computer-science |

| keywords[1].score | 0.7024036645889282 |

| keywords[1].display_name | Computer science |

| keywords[2].id | https://openalex.org/keywords/embedded-system |

| keywords[2].score | 0.6250280141830444 |

| keywords[2].display_name | Embedded system |

| keywords[3].id | https://openalex.org/keywords/computer-hardware |

| keywords[3].score | 0.624546229839325 |

| keywords[3].display_name | Computer hardware |

| keywords[4].id | https://openalex.org/keywords/field-programmable-gate-array |

| keywords[4].score | 0.5850247144699097 |

| keywords[4].display_name | Field-programmable gate array |

| keywords[5].id | https://openalex.org/keywords/serial-communication |

| keywords[5].score | 0.503497302532196 |

| keywords[5].display_name | Serial communication |

| keywords[6].id | https://openalex.org/keywords/adapter |

| keywords[6].score | 0.4968924820423126 |

| keywords[6].display_name | Adapter (computing) |

| keywords[7].id | https://openalex.org/keywords/application-specific-integrated-circuit |

| keywords[7].score | 0.4569379389286041 |

| keywords[7].display_name | Application-specific integrated circuit |

| keywords[8].id | https://openalex.org/keywords/gate-array |

| keywords[8].score | 0.44805407524108887 |

| keywords[8].display_name | Gate array |

| keywords[9].id | https://openalex.org/keywords/interface |

| keywords[9].score | 0.44588953256607056 |

| keywords[9].display_name | Interface (matter) |

| keywords[10].id | https://openalex.org/keywords/handshake |

| keywords[10].score | 0.41299179196357727 |

| keywords[10].display_name | Handshake |

| keywords[11].id | https://openalex.org/keywords/asynchronous-communication |

| keywords[11].score | 0.4104264974594116 |

| keywords[11].display_name | Asynchronous communication |

| keywords[12].id | https://openalex.org/keywords/computer-network |

| keywords[12].score | 0.316172331571579 |

| keywords[12].display_name | Computer network |

| keywords[13].id | https://openalex.org/keywords/operating-system |

| keywords[13].score | 0.12389713525772095 |

| keywords[13].display_name | Operating system |

| language | en |

| locations[0].id | doi:10.1063/5.0109796 |

| locations[0].is_oa | True |

| locations[0].source.id | https://openalex.org/S2764696622 |

| locations[0].source.issn | 0094-243X, 1551-7616, 1935-0465 |

| locations[0].source.type | journal |

| locations[0].source.is_oa | False |

| locations[0].source.issn_l | 0094-243X |

| locations[0].source.is_core | True |

| locations[0].source.is_in_doaj | False |

| locations[0].source.display_name | AIP conference proceedings |

| locations[0].source.host_organization | https://openalex.org/P4310320257 |

| locations[0].source.host_organization_name | American Institute of Physics |

| locations[0].source.host_organization_lineage | https://openalex.org/P4310320257 |

| locations[0].source.host_organization_lineage_names | American Institute of Physics |

| locations[0].license | |

| locations[0].pdf_url | https://aip.scitation.org/doi/pdf/10.1063/5.0109796 |

| locations[0].version | publishedVersion |

| locations[0].raw_type | proceedings-article |

| locations[0].license_id | |

| locations[0].is_accepted | True |

| locations[0].is_published | True |

| locations[0].raw_source_name | AIP Conference Proceedings |

| locations[0].landing_page_url | https://doi.org/10.1063/5.0109796 |

| indexed_in | crossref |

| authorships[0].author.id | https://openalex.org/A5056315144 |

| authorships[0].author.orcid | |

| authorships[0].author.display_name | S. Mahaboob Basha |

| authorships[0].affiliations[0].institution_ids | https://openalex.org/I4387154816 |

| authorships[0].affiliations[0].raw_affiliation_string | ,3Department of Electronics and Communication Engineering, R.M.K. Engineering College, R.S.M Nigar, Kavaraipettai, Tamilnadu, India |

| authorships[0].institutions[0].id | https://openalex.org/I4387154816 |

| authorships[0].institutions[0].ror | https://ror.org/03gjktv92 |

| authorships[0].institutions[0].type | education |

| authorships[0].institutions[0].lineage | https://openalex.org/I4387154816 |

| authorships[0].institutions[0].country_code | |

| authorships[0].institutions[0].display_name | R.M.D. Engineering College |

| authorships[0].author_position | first |

| authorships[0].raw_author_name | S. Mahaboob Basha |

| authorships[0].is_corresponding | True |

| authorships[0].raw_affiliation_strings | ,3Department of Electronics and Communication Engineering, R.M.K. Engineering College, R.S.M Nigar, Kavaraipettai, Tamilnadu, India |

| authorships[1].author.id | https://openalex.org/A5101409480 |

| authorships[1].author.orcid | |

| authorships[1].author.display_name | A. Arun |

| authorships[1].countries | IN |

| authorships[1].affiliations[0].institution_ids | https://openalex.org/I145286018 |

| authorships[1].affiliations[0].raw_affiliation_string | Department of Computer Science and Engineering, SRM Institute of Science and Technology, SRM Nagar, Kattankulathur, Kanchipuram, Chennai, Tamil Nadu, India |

| authorships[1].institutions[0].id | https://openalex.org/I145286018 |

| authorships[1].institutions[0].ror | https://ror.org/050113w36 |

| authorships[1].institutions[0].type | education |

| authorships[1].institutions[0].lineage | https://openalex.org/I145286018 |

| authorships[1].institutions[0].country_code | IN |

| authorships[1].institutions[0].display_name | SRM Institute of Science and Technology |

| authorships[1].author_position | middle |

| authorships[1].raw_author_name | A. Arun |

| authorships[1].is_corresponding | False |

| authorships[1].raw_affiliation_strings | Department of Computer Science and Engineering, SRM Institute of Science and Technology, SRM Nagar, Kattankulathur, Kanchipuram, Chennai, Tamil Nadu, India |

| authorships[2].author.id | https://openalex.org/A5025866698 |

| authorships[2].author.orcid | |

| authorships[2].author.display_name | T.D. Subha |

| authorships[2].countries | IN |

| authorships[2].affiliations[0].institution_ids | https://openalex.org/I145286018 |

| authorships[2].affiliations[0].raw_affiliation_string | Department of Electronics and Communication Engineering, SRM Institute of Science and Technology, City Campus, Vadapalani, Chennai, Tamil Nadu, India |

| authorships[2].institutions[0].id | https://openalex.org/I145286018 |

| authorships[2].institutions[0].ror | https://ror.org/050113w36 |

| authorships[2].institutions[0].type | education |

| authorships[2].institutions[0].lineage | https://openalex.org/I145286018 |

| authorships[2].institutions[0].country_code | IN |

| authorships[2].institutions[0].display_name | SRM Institute of Science and Technology |

| authorships[2].author_position | middle |

| authorships[2].raw_author_name | T. D. Subha |

| authorships[2].is_corresponding | False |

| authorships[2].raw_affiliation_strings | Department of Electronics and Communication Engineering, SRM Institute of Science and Technology, City Campus, Vadapalani, Chennai, Tamil Nadu, India |

| authorships[3].author.id | https://openalex.org/A5066585136 |

| authorships[3].author.orcid | |

| authorships[3].author.display_name | V. Bhuvaneswari |

| authorships[3].countries | IN |

| authorships[3].affiliations[0].institution_ids | https://openalex.org/I145286018 |

| authorships[3].affiliations[0].raw_affiliation_string | Department of Electronics and Communication Engineering, SRM Institute of Science and Technology, City Campus, Vadapalani, Chennai, Tamil Nadu, India |

| authorships[3].institutions[0].id | https://openalex.org/I145286018 |

| authorships[3].institutions[0].ror | https://ror.org/050113w36 |

| authorships[3].institutions[0].type | education |

| authorships[3].institutions[0].lineage | https://openalex.org/I145286018 |

| authorships[3].institutions[0].country_code | IN |

| authorships[3].institutions[0].display_name | SRM Institute of Science and Technology |

| authorships[3].author_position | middle |

| authorships[3].raw_author_name | V. Bhuvaneswari |

| authorships[3].is_corresponding | False |

| authorships[3].raw_affiliation_strings | Department of Electronics and Communication Engineering, SRM Institute of Science and Technology, City Campus, Vadapalani, Chennai, Tamil Nadu, India |

| authorships[4].author.id | https://openalex.org/A5066137238 |

| authorships[4].author.orcid | |

| authorships[4].author.display_name | D. Kalai Selvi |

| authorships[4].countries | IN |

| authorships[4].affiliations[0].institution_ids | https://openalex.org/I145286018 |

| authorships[4].affiliations[0].raw_affiliation_string | Department of Electronics and Communication Engineering, SRM Institute of Science and Technology, City Campus, Vadapalani, Chennai, Tamil Nadu, India |

| authorships[4].institutions[0].id | https://openalex.org/I145286018 |

| authorships[4].institutions[0].ror | https://ror.org/050113w36 |

| authorships[4].institutions[0].type | education |

| authorships[4].institutions[0].lineage | https://openalex.org/I145286018 |

| authorships[4].institutions[0].country_code | IN |

| authorships[4].institutions[0].display_name | SRM Institute of Science and Technology |

| authorships[4].author_position | middle |

| authorships[4].raw_author_name | D. Kalai Selvi |

| authorships[4].is_corresponding | False |

| authorships[4].raw_affiliation_strings | Department of Electronics and Communication Engineering, SRM Institute of Science and Technology, City Campus, Vadapalani, Chennai, Tamil Nadu, India |

| authorships[5].author.id | https://openalex.org/A5034486566 |

| authorships[5].author.orcid | |

| authorships[5].author.display_name | J. Nain Sankar |

| authorships[5].affiliations[0].raw_affiliation_string | Entuple Technologies Pvt Ltd, Bangalore, Karnataka, India |

| authorships[5].author_position | last |

| authorships[5].raw_author_name | J. Nain Sankar |

| authorships[5].is_corresponding | False |

| authorships[5].raw_affiliation_strings | Entuple Technologies Pvt Ltd, Bangalore, Karnataka, India |

| has_content.pdf | True |

| has_content.grobid_xml | True |

| is_paratext | False |

| open_access.is_oa | True |

| open_access.oa_url | https://aip.scitation.org/doi/pdf/10.1063/5.0109796 |

| open_access.oa_status | bronze |

| open_access.any_repository_has_fulltext | False |

| created_date | 2025-10-10T00:00:00 |

| display_name | FPGA implementation of integrated circuit interactions along with modem connectivity and adapter transponder |

| has_fulltext | False |

| is_retracted | False |

| updated_date | 2025-11-06T03:46:38.306776 |

| primary_topic.id | https://openalex.org/T12941 |

| primary_topic.field.id | https://openalex.org/fields/22 |

| primary_topic.field.display_name | Engineering |

| primary_topic.score | 0.9965000152587891 |

| primary_topic.domain.id | https://openalex.org/domains/3 |

| primary_topic.domain.display_name | Physical Sciences |

| primary_topic.subfield.id | https://openalex.org/subfields/2207 |

| primary_topic.subfield.display_name | Control and Systems Engineering |

| primary_topic.display_name | Embedded Systems and FPGA Design |

| related_works | https://openalex.org/W2380027653, https://openalex.org/W2335461561, https://openalex.org/W4385374337, https://openalex.org/W4252733581, https://openalex.org/W2381196179, https://openalex.org/W3012774222, https://openalex.org/W2372225036, https://openalex.org/W4235021281, https://openalex.org/W2110115737, https://openalex.org/W2086724687 |

| cited_by_count | 1 |

| counts_by_year[0].year | 2023 |

| counts_by_year[0].cited_by_count | 1 |

| locations_count | 1 |

| best_oa_location.id | doi:10.1063/5.0109796 |

| best_oa_location.is_oa | True |

| best_oa_location.source.id | https://openalex.org/S2764696622 |

| best_oa_location.source.issn | 0094-243X, 1551-7616, 1935-0465 |

| best_oa_location.source.type | journal |

| best_oa_location.source.is_oa | False |

| best_oa_location.source.issn_l | 0094-243X |

| best_oa_location.source.is_core | True |

| best_oa_location.source.is_in_doaj | False |

| best_oa_location.source.display_name | AIP conference proceedings |

| best_oa_location.source.host_organization | https://openalex.org/P4310320257 |

| best_oa_location.source.host_organization_name | American Institute of Physics |

| best_oa_location.source.host_organization_lineage | https://openalex.org/P4310320257 |

| best_oa_location.source.host_organization_lineage_names | American Institute of Physics |

| best_oa_location.license | |

| best_oa_location.pdf_url | https://aip.scitation.org/doi/pdf/10.1063/5.0109796 |

| best_oa_location.version | publishedVersion |

| best_oa_location.raw_type | proceedings-article |

| best_oa_location.license_id | |

| best_oa_location.is_accepted | True |

| best_oa_location.is_published | True |

| best_oa_location.raw_source_name | AIP Conference Proceedings |

| best_oa_location.landing_page_url | https://doi.org/10.1063/5.0109796 |

| primary_location.id | doi:10.1063/5.0109796 |

| primary_location.is_oa | True |

| primary_location.source.id | https://openalex.org/S2764696622 |

| primary_location.source.issn | 0094-243X, 1551-7616, 1935-0465 |

| primary_location.source.type | journal |

| primary_location.source.is_oa | False |

| primary_location.source.issn_l | 0094-243X |

| primary_location.source.is_core | True |

| primary_location.source.is_in_doaj | False |

| primary_location.source.display_name | AIP conference proceedings |

| primary_location.source.host_organization | https://openalex.org/P4310320257 |

| primary_location.source.host_organization_name | American Institute of Physics |

| primary_location.source.host_organization_lineage | https://openalex.org/P4310320257 |

| primary_location.source.host_organization_lineage_names | American Institute of Physics |

| primary_location.license | |

| primary_location.pdf_url | https://aip.scitation.org/doi/pdf/10.1063/5.0109796 |

| primary_location.version | publishedVersion |

| primary_location.raw_type | proceedings-article |

| primary_location.license_id | |

| primary_location.is_accepted | True |

| primary_location.is_published | True |

| primary_location.raw_source_name | AIP Conference Proceedings |

| primary_location.landing_page_url | https://doi.org/10.1063/5.0109796 |

| publication_date | 2022-01-01 |

| publication_year | 2022 |

| referenced_works | https://openalex.org/W2610905138, https://openalex.org/W1992900191, https://openalex.org/W3102923738, https://openalex.org/W2164353558, https://openalex.org/W2811259659, https://openalex.org/W3032384272, https://openalex.org/W2119066200, https://openalex.org/W2774205278, https://openalex.org/W3112642478, https://openalex.org/W3091619519, https://openalex.org/W2073238650, https://openalex.org/W2041273742, https://openalex.org/W2013912619, https://openalex.org/W3031379747, https://openalex.org/W2027106468, https://openalex.org/W3029217266 |

| referenced_works_count | 16 |

| abstract_inverted_index.V | 189 |

| abstract_inverted_index.a | 182 |

| abstract_inverted_index.38 | 191 |

| abstract_inverted_index.as | 40, 42, 61, 120 |

| abstract_inverted_index.at | 181 |

| abstract_inverted_index.be | 30 |

| abstract_inverted_index.in | 5, 20, 71, 109, 133 |

| abstract_inverted_index.is | 18, 69, 93, 98, 107, 130, 153, 161, 173, 179 |

| abstract_inverted_index.mW | 175 |

| abstract_inverted_index.of | 2, 35, 56, 82, 88, 166, 171, 187 |

| abstract_inverted_index.on | 122 |

| abstract_inverted_index.so | 44 |

| abstract_inverted_index.to | 28, 101, 134 |

| abstract_inverted_index.1.8 | 188 |

| abstract_inverted_index.2Kb | 67 |

| abstract_inverted_index.SIE | 24 |

| abstract_inverted_index.The | 0, 23, 113, 127 |

| abstract_inverted_index.USB | 10, 110 |

| abstract_inverted_index.and | 16, 176, 184, 190 |

| abstract_inverted_index.are | 117, 168 |

| abstract_inverted_index.but | 64 |

| abstract_inverted_index.for | 124 |

| abstract_inverted_index.has | 146 |

| abstract_inverted_index.pin | 185 |

| abstract_inverted_index.the | 47, 105, 140, 177 |

| abstract_inverted_index.use | 139 |

| abstract_inverted_index.via | 9 |

| abstract_inverted_index.FIFO | 17 |

| abstract_inverted_index.FPGA | 77 |

| abstract_inverted_index.PC's | 36 |

| abstract_inverted_index.PISO | 91 |

| abstract_inverted_index.SIPO | 141 |

| abstract_inverted_index.also | 29, 65 |

| abstract_inverted_index.been | 147 |

| abstract_inverted_index.care | 55 |

| abstract_inverted_index.data | 4, 63, 81, 87, 114, 145, 150 |

| abstract_inverted_index.form | 84 |

| abstract_inverted_index.from | 32 |

| abstract_inverted_index.gate | 7 |

| abstract_inverted_index.into | 85 |

| abstract_inverted_index.kind | 34 |

| abstract_inverted_index.make | 102 |

| abstract_inverted_index.many | 45, 57 |

| abstract_inverted_index.once | 144 |

| abstract_inverted_index.some | 33 |

| abstract_inverted_index.such | 60 |

| abstract_inverted_index.sure | 103 |

| abstract_inverted_index.that | 53, 104, 138, 143 |

| abstract_inverted_index.then | 131 |

| abstract_inverted_index.this | 21 |

| abstract_inverted_index.unit | 39 |

| abstract_inverted_index.used | 100 |

| abstract_inverted_index.well | 41 |

| abstract_inverted_index.with | 12 |

| abstract_inverted_index.50MHz | 180 |

| abstract_inverted_index.ASIC) | 160 |

| abstract_inverted_index.array | 8 |

| abstract_inverted_index.based | 121 |

| abstract_inverted_index.being | 99 |

| abstract_inverted_index.form, | 90 |

| abstract_inverted_index.gates | 167 |

| abstract_inverted_index.input | 80 |

| abstract_inverted_index.other | 135 |

| abstract_inverted_index.power | 172 |

| abstract_inverted_index.queue | 68 |

| abstract_inverted_index.takes | 54 |

| abstract_inverted_index.used. | 94 |

| abstract_inverted_index.2.6742 | 174 |

| abstract_inverted_index.Device | 95 |

| abstract_inverted_index.cyclic | 125 |

| abstract_inverted_index.device | 158 |

| abstract_inverted_index.engine | 15 |

| abstract_inverted_index.inputs | 27 |

| abstract_inverted_index.number | 165 |

| abstract_inverted_index.output | 86 |

| abstract_inverted_index.paper. | 22 |

| abstract_inverted_index.passes | 43 |

| abstract_inverted_index.serial | 13, 89 |

| abstract_inverted_index.signal | 129 |

| abstract_inverted_index.system | 152 |

| abstract_inverted_index.14,547, | 169 |

| abstract_inverted_index.already | 108 |

| abstract_inverted_index.between | 75 |

| abstract_inverted_index.convert | 79 |

| abstract_inverted_index.created | 162 |

| abstract_inverted_index.numbers | 186 |

| abstract_inverted_index.process | 1 |

| abstract_inverted_index.routing | 111 |

| abstract_inverted_index.signals | 137 |

| abstract_inverted_index.through | 46 |

| abstract_inverted_index.voltage | 183 |

| abstract_inverted_index.working | 154 |

| abstract_inverted_index.(example | 159 |

| abstract_inverted_index.assuring | 72 |

| abstract_inverted_index.cellular | 51 |

| abstract_inverted_index.checking | 115 |

| abstract_inverted_index.concerns | 59 |

| abstract_inverted_index.expected | 123 |

| abstract_inverted_index.incoming | 128 |

| abstract_inverted_index.multiple | 76 |

| abstract_inverted_index.parallel | 83 |

| abstract_inverted_index.prepared | 70 |

| abstract_inverted_index.component | 25, 142 |

| abstract_inverted_index.connected | 11 |

| abstract_inverted_index.converter | 92 |

| abstract_inverted_index.effective | 73 |

| abstract_inverted_index.frequency | 178 |

| abstract_inverted_index.generally | 118 |

| abstract_inverted_index.interface | 14 |

| abstract_inverted_index.presented | 19 |

| abstract_inverted_index.processor | 38 |

| abstract_inverted_index.protocol. | 112 |

| abstract_inverted_index.transmits | 26 |

| abstract_inverted_index.utilizing | 163 |

| abstract_inverted_index.assertions | 116 |

| abstract_inverted_index.electronic | 136, 157 |

| abstract_inverted_index.interface, | 52 |

| abstract_inverted_index.Information | 96 |

| abstract_inverted_index.categorized | 119 |

| abstract_inverted_index.centralized | 37 |

| abstract_inverted_index.consumption | 170 |

| abstract_inverted_index.information | 106 |

| abstract_inverted_index.properly.An | 155 |

| abstract_inverted_index.transformed | 132 |

| abstract_inverted_index.FPGA-to-FPGA | 149 |

| abstract_inverted_index.Notification | 97 |

| abstract_inverted_index.analyzed.The | 148 |

| abstract_inverted_index.communicated | 31 |

| abstract_inverted_index.consistency. | 126 |

| abstract_inverted_index.conventional | 50 |

| abstract_inverted_index.conversation | 74 |

| abstract_inverted_index.standardized | 48 |

| abstract_inverted_index.transmission | 49, 151 |

| abstract_inverted_index.transmitting | 3, 62 |

| abstract_inverted_index.processors.To | 78 |

| abstract_inverted_index.respectively. | 192 |

| abstract_inverted_index.Transistor.The | 164 |

| abstract_inverted_index.implementation | 156 |

| abstract_inverted_index.rehabilitation.A | 66 |

| abstract_inverted_index.field-programmable | 6 |

| abstract_inverted_index.transmission-related | 58 |

| cited_by_percentile_year.max | 94 |

| cited_by_percentile_year.min | 89 |

| corresponding_author_ids | https://openalex.org/A5056315144 |

| countries_distinct_count | 1 |

| institutions_distinct_count | 6 |

| corresponding_institution_ids | https://openalex.org/I4387154816 |

| sustainable_development_goals[0].id | https://metadata.un.org/sdg/7 |

| sustainable_development_goals[0].score | 0.7699999809265137 |

| sustainable_development_goals[0].display_name | Affordable and clean energy |

| citation_normalized_percentile.value | 0.46138982 |

| citation_normalized_percentile.is_in_top_1_percent | False |

| citation_normalized_percentile.is_in_top_10_percent | False |