HIGH SPEED ADDER USING GDI TECHNIQUE Article Swipe

Related Concepts

Adder

Computer science

Electronic engineering

Electronic circuit

Power consumption

Power–delay product

Serial binary adder

Digital electronics

Carry-save adder

Logic gate

Power (physics)

Arithmetic

Computer hardware

Electrical engineering

Engineering

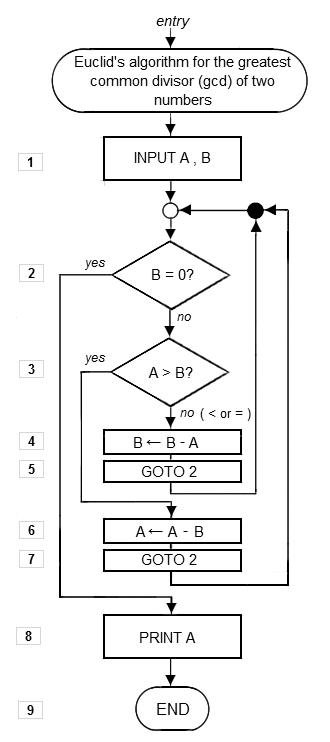

Algorithm

CMOS

Mathematics

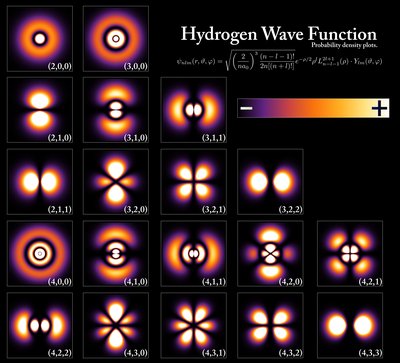

Quantum mechanics

Physics

Merrin Mary Solomon

,

Neeraj Gupta

,

Rashmi Gupta

·

YOU?

·

· 2020

· Open Access

·

· DOI: https://doi.org/10.29121/ijetmr.v5.i2.2018.634

· OA: W3023152331

YOU?

·

· 2020

· Open Access

·

· DOI: https://doi.org/10.29121/ijetmr.v5.i2.2018.634

· OA: W3023152331

YOU?

·

· 2020

· Open Access

·

· DOI: https://doi.org/10.29121/ijetmr.v5.i2.2018.634

· OA: W3023152331

YOU?

·

· 2020

· Open Access

·

· DOI: https://doi.org/10.29121/ijetmr.v5.i2.2018.634

· OA: W3023152331

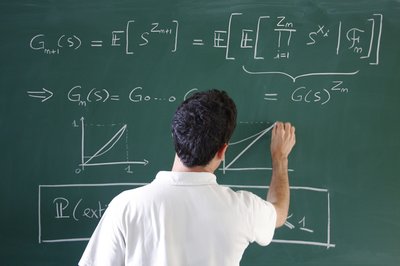

Full adder is an important component for designing a processor. As the complexity of the circuit increases, the speed of operation becomes a major concern. Nowadays there are various architectures that exist for full adders. In this paper we will discuss about designing a low power and high speed full adder using Gate Diffusion Input technique. GDI is one of the present day methods through which one can design logical circuits. This technique will reduce power consumption, propagation delay, and area of digital circuits as well as maintain low complexity of logic design. The performance of the proposed design is compared with the contemporary full adder designs.

Related Topics

Finding more related topics…