Hardware-Assisted Thread and Data Mapping in Hierarchical Multicore Architectures Article Swipe

Related Concepts

Translation lookaside buffer

Computer science

Locality

Thread (computing)

Locality of reference

Parallel computing

Cache

Physical address

Page

CPU cache

Interconnection

False sharing

Memory hierarchy

Computer architecture

Distributed computing

Embedded system

Cache algorithms

Operating system

Computer network

Semiconductor memory

Linguistics

Philosophy

Eduardo H. M. Cruz

,

Matthias Diener

,

Laércio Lima Pilla

,

Philippe O. A. Navaux

·

YOU?

·

· 2016

· Open Access

·

· DOI: https://doi.org/10.1145/2975587

· OA: W2521259554

YOU?

·

· 2016

· Open Access

·

· DOI: https://doi.org/10.1145/2975587

· OA: W2521259554

YOU?

·

· 2016

· Open Access

·

· DOI: https://doi.org/10.1145/2975587

· OA: W2521259554

YOU?

·

· 2016

· Open Access

·

· DOI: https://doi.org/10.1145/2975587

· OA: W2521259554

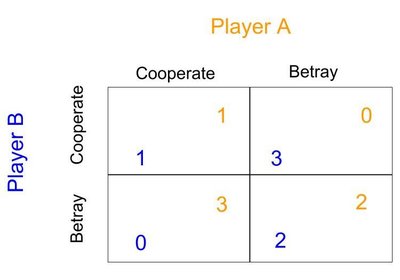

The performance and energy efficiency of modern architectures depend on memory locality, which can be improved by thread and data mappings considering the memory access behavior of parallel applications. In this article, we propose intense pages mapping, a mechanism that analyzes the memory access behavior using information about the time the entry of each page resides in the translation lookaside buffer. It provides accurate information with a very low overhead. We present experimental results with simulation and real machines, with average performance improvements of 13.7% and energy savings of 4.4%, which come from reductions in cache misses and interconnection traffic.

Related Topics

Finding more related topics…