FAULT-TOLERANT SELT-TIMED COUNTERS Article Swipe

YOU?

·

· 2023

· Open Access

·

· DOI: https://doi.org/10.29003/m3614.mmmsec-2023/167-170

· OA: W4387906791

YOU?

·

· 2023

· Open Access

·

· DOI: https://doi.org/10.29003/m3614.mmmsec-2023/167-170

· OA: W4387906791

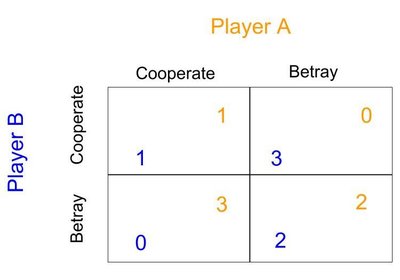

The article studies the fault-tolerant self-timed (ST) counter design problem. Combinational ST circuits have a higher fault tolerance in comparison with synchronous counterparts due to redundant information coding and mandatory acknowledging of the completion of all initiated circuit cells' switches. Sequential ST circuits, including counters, are more sensitive to failures due to the presence of memory cells, the state of which can change under the influence of a failure and be remembered. For their fault-tolerant implementation, special circuitry methods, namely DICE and Quatro, are used. These approaches significantly reduces the likelihood of a change in the counter bit's state due to a failure. The article proposes DICE-type and Quatro-type ST counter cases, compares their features and gives recommendations for the fault-tolerant ST counter implementation