Senary Hypercubic Computational Logic Architecture: A Full Academic Suite with Verilog HDL Article Swipe

JUDE, ALEXANDRU-BOGDAN

·

YOU?

·

· 2025

· Open Access

·

· DOI: https://doi.org/10.5281/zenodo.17813133

YOU?

·

· 2025

· Open Access

·

· DOI: https://doi.org/10.5281/zenodo.17813133

YOU?

·

· 2025

· Open Access

·

· DOI: https://doi.org/10.5281/zenodo.17813133

YOU?

·

· 2025

· Open Access

·

· DOI: https://doi.org/10.5281/zenodo.17813133

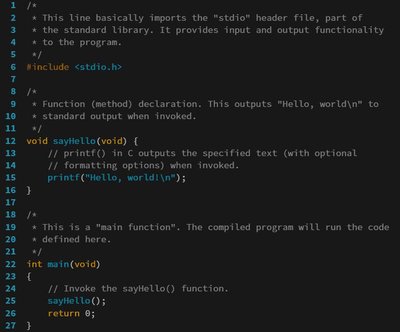

This record presents the complete Senary Electron Paradigm and its implementation. The submission includes the core theoretical paper, a comprehensive Verilog HDL Blueprints Suite for the Sixtinary CPU (including arithmetic, token routing, face mapping, and testbenches), and two distinct Python Simulators. The main simulator, sixtaidryson pigamafi.py, implements the integration of fundamental irrational **Cosmic Constants (Pi, Gamma, Phi)** to establish a theoretical framework for **Coherence and Rate Control** within the architecture.

Related Topics

Concepts

Metadata

- Type

- article

- Landing Page

- https://doi.org/10.5281/zenodo.17813133

- OA Status

- green

- OpenAlex ID

- https://openalex.org/W7108746302

All OpenAlex metadata

Raw OpenAlex JSON

- OpenAlex ID

-

https://openalex.org/W7108746302Canonical identifier for this work in OpenAlex

- DOI

-

https://doi.org/10.5281/zenodo.17813133Digital Object Identifier

- Title

-

Senary Hypercubic Computational Logic Architecture: A Full Academic Suite with Verilog HDLWork title

- Type

-

articleOpenAlex work type

- Publication year

-

2025Year of publication

- Publication date

-

2025-12-04Full publication date if available

- Authors

-

JUDE, ALEXANDRU-BOGDANList of authors in order

- Landing page

-

https://doi.org/10.5281/zenodo.17813133Publisher landing page

- Open access

-

YesWhether a free full text is available

- OA status

-

greenOpen access status per OpenAlex

- OA URL

-

https://doi.org/10.5281/zenodo.17813133Direct OA link when available

- Concepts

-

Computer science, Suite, Verilog, Programming language, Python (programming language), Theoretical computer science, Security token, Parallel computing, Blueprint, Computer architecture, USable, Adder, Correctness, Core (optical fiber), Arithmetic, Logic synthesisTop concepts (fields/topics) attached by OpenAlex

- Cited by

-

0Total citation count in OpenAlex

Full payload

| id | https://openalex.org/W7108746302 |

|---|---|

| doi | https://doi.org/10.5281/zenodo.17813133 |

| ids.doi | https://doi.org/10.5281/zenodo.17813133 |

| ids.openalex | https://openalex.org/W7108746302 |

| fwci | 0.0 |

| type | article |

| title | Senary Hypercubic Computational Logic Architecture: A Full Academic Suite with Verilog HDL |

| biblio.issue | |

| biblio.volume | |

| biblio.last_page | |

| biblio.first_page | |

| topics[0].id | https://openalex.org/T13182 |

| topics[0].field.id | https://openalex.org/fields/17 |

| topics[0].field.display_name | Computer Science |

| topics[0].score | 0.1354302018880844 |

| topics[0].domain.id | https://openalex.org/domains/3 |

| topics[0].domain.display_name | Physical Sciences |

| topics[0].subfield.id | https://openalex.org/subfields/1703 |

| topics[0].subfield.display_name | Computational Theory and Mathematics |

| topics[0].display_name | Quantum-Dot Cellular Automata |

| topics[1].id | https://openalex.org/T13436 |

| topics[1].field.id | https://openalex.org/fields/22 |

| topics[1].field.display_name | Engineering |

| topics[1].score | 0.09724502265453339 |

| topics[1].domain.id | https://openalex.org/domains/3 |

| topics[1].domain.display_name | Physical Sciences |

| topics[1].subfield.id | https://openalex.org/subfields/2208 |

| topics[1].subfield.display_name | Electrical and Electronic Engineering |

| topics[1].display_name | Space Technology and Applications |

| topics[2].id | https://openalex.org/T13292 |

| topics[2].field.id | https://openalex.org/fields/22 |

| topics[2].field.display_name | Engineering |

| topics[2].score | 0.0771992951631546 |

| topics[2].domain.id | https://openalex.org/domains/3 |

| topics[2].domain.display_name | Physical Sciences |

| topics[2].subfield.id | https://openalex.org/subfields/2208 |

| topics[2].subfield.display_name | Electrical and Electronic Engineering |

| topics[2].display_name | Embedded Systems and FPGA Applications |

| is_xpac | False |

| apc_list | |

| apc_paid | |

| concepts[0].id | https://openalex.org/C41008148 |

| concepts[0].level | 0 |

| concepts[0].score | 0.811395525932312 |

| concepts[0].wikidata | https://www.wikidata.org/wiki/Q21198 |

| concepts[0].display_name | Computer science |

| concepts[1].id | https://openalex.org/C79581498 |

| concepts[1].level | 2 |

| concepts[1].score | 0.7649058103561401 |

| concepts[1].wikidata | https://www.wikidata.org/wiki/Q1367530 |

| concepts[1].display_name | Suite |

| concepts[2].id | https://openalex.org/C2779030575 |

| concepts[2].level | 3 |

| concepts[2].score | 0.6999689340591431 |

| concepts[2].wikidata | https://www.wikidata.org/wiki/Q827773 |

| concepts[2].display_name | Verilog |

| concepts[3].id | https://openalex.org/C199360897 |

| concepts[3].level | 1 |

| concepts[3].score | 0.6339190006256104 |

| concepts[3].wikidata | https://www.wikidata.org/wiki/Q9143 |

| concepts[3].display_name | Programming language |

| concepts[4].id | https://openalex.org/C519991488 |

| concepts[4].level | 2 |

| concepts[4].score | 0.5666424632072449 |

| concepts[4].wikidata | https://www.wikidata.org/wiki/Q28865 |

| concepts[4].display_name | Python (programming language) |

| concepts[5].id | https://openalex.org/C80444323 |

| concepts[5].level | 1 |

| concepts[5].score | 0.4083326756954193 |

| concepts[5].wikidata | https://www.wikidata.org/wiki/Q2878974 |

| concepts[5].display_name | Theoretical computer science |

| concepts[6].id | https://openalex.org/C48145219 |

| concepts[6].level | 2 |

| concepts[6].score | 0.3914536237716675 |

| concepts[6].wikidata | https://www.wikidata.org/wiki/Q1335365 |

| concepts[6].display_name | Security token |

| concepts[7].id | https://openalex.org/C173608175 |

| concepts[7].level | 1 |

| concepts[7].score | 0.3765662610530853 |

| concepts[7].wikidata | https://www.wikidata.org/wiki/Q232661 |

| concepts[7].display_name | Parallel computing |

| concepts[8].id | https://openalex.org/C155911762 |

| concepts[8].level | 2 |

| concepts[8].score | 0.3620125353336334 |

| concepts[8].wikidata | https://www.wikidata.org/wiki/Q422321 |

| concepts[8].display_name | Blueprint |

| concepts[9].id | https://openalex.org/C118524514 |

| concepts[9].level | 1 |

| concepts[9].score | 0.34348583221435547 |

| concepts[9].wikidata | https://www.wikidata.org/wiki/Q173212 |

| concepts[9].display_name | Computer architecture |

| concepts[10].id | https://openalex.org/C2780615836 |

| concepts[10].level | 2 |

| concepts[10].score | 0.3391031324863434 |

| concepts[10].wikidata | https://www.wikidata.org/wiki/Q2471869 |

| concepts[10].display_name | USable |

| concepts[11].id | https://openalex.org/C164620267 |

| concepts[11].level | 3 |

| concepts[11].score | 0.333236962556839 |

| concepts[11].wikidata | https://www.wikidata.org/wiki/Q376953 |

| concepts[11].display_name | Adder |

| concepts[12].id | https://openalex.org/C55439883 |

| concepts[12].level | 2 |

| concepts[12].score | 0.32310307025909424 |

| concepts[12].wikidata | https://www.wikidata.org/wiki/Q360812 |

| concepts[12].display_name | Correctness |

| concepts[13].id | https://openalex.org/C2164484 |

| concepts[13].level | 2 |

| concepts[13].score | 0.28472787141799927 |

| concepts[13].wikidata | https://www.wikidata.org/wiki/Q5170150 |

| concepts[13].display_name | Core (optical fiber) |

| concepts[14].id | https://openalex.org/C94375191 |

| concepts[14].level | 1 |

| concepts[14].score | 0.2549215257167816 |

| concepts[14].wikidata | https://www.wikidata.org/wiki/Q11205 |

| concepts[14].display_name | Arithmetic |

| concepts[15].id | https://openalex.org/C157922185 |

| concepts[15].level | 3 |

| concepts[15].score | 0.2507115304470062 |

| concepts[15].wikidata | https://www.wikidata.org/wiki/Q173198 |

| concepts[15].display_name | Logic synthesis |

| keywords[0].id | https://openalex.org/keywords/suite |

| keywords[0].score | 0.7649058103561401 |

| keywords[0].display_name | Suite |

| keywords[1].id | https://openalex.org/keywords/verilog |

| keywords[1].score | 0.6999689340591431 |

| keywords[1].display_name | Verilog |

| keywords[2].id | https://openalex.org/keywords/python |

| keywords[2].score | 0.5666424632072449 |

| keywords[2].display_name | Python (programming language) |

| keywords[3].id | https://openalex.org/keywords/security-token |

| keywords[3].score | 0.3914536237716675 |

| keywords[3].display_name | Security token |

| keywords[4].id | https://openalex.org/keywords/blueprint |

| keywords[4].score | 0.3620125353336334 |

| keywords[4].display_name | Blueprint |

| keywords[5].id | https://openalex.org/keywords/usable |

| keywords[5].score | 0.3391031324863434 |

| keywords[5].display_name | USable |

| language | |

| locations[0].id | doi:10.5281/zenodo.17813133 |

| locations[0].is_oa | True |

| locations[0].source.id | https://openalex.org/S4306400562 |

| locations[0].source.issn | |

| locations[0].source.type | repository |

| locations[0].source.is_oa | True |

| locations[0].source.issn_l | |

| locations[0].source.is_core | False |

| locations[0].source.is_in_doaj | False |

| locations[0].source.display_name | Zenodo (CERN European Organization for Nuclear Research) |

| locations[0].source.host_organization | https://openalex.org/I67311998 |

| locations[0].source.host_organization_name | European Organization for Nuclear Research |

| locations[0].source.host_organization_lineage | https://openalex.org/I67311998 |

| locations[0].license | |

| locations[0].pdf_url | |

| locations[0].version | |

| locations[0].raw_type | article-journal |

| locations[0].license_id | |

| locations[0].is_accepted | False |

| locations[0].is_published | |

| locations[0].raw_source_name | |

| locations[0].landing_page_url | https://doi.org/10.5281/zenodo.17813133 |

| indexed_in | datacite |

| authorships[0].author.id | |

| authorships[0].author.orcid | |

| authorships[0].author.display_name | JUDE, ALEXANDRU-BOGDAN |

| authorships[0].author_position | first |

| authorships[0].raw_author_name | JUDE, ALEXANDRU-BOGDAN |

| authorships[0].is_corresponding | True |

| has_content.pdf | False |

| has_content.grobid_xml | False |

| is_paratext | False |

| open_access.is_oa | True |

| open_access.oa_url | https://doi.org/10.5281/zenodo.17813133 |

| open_access.oa_status | green |

| open_access.any_repository_has_fulltext | False |

| created_date | 2025-12-05T00:00:00 |

| display_name | Senary Hypercubic Computational Logic Architecture: A Full Academic Suite with Verilog HDL |

| has_fulltext | False |

| is_retracted | False |

| updated_date | 2025-12-08T23:20:48.110394 |

| primary_topic.id | https://openalex.org/T13182 |

| primary_topic.field.id | https://openalex.org/fields/17 |

| primary_topic.field.display_name | Computer Science |

| primary_topic.score | 0.1354302018880844 |

| primary_topic.domain.id | https://openalex.org/domains/3 |

| primary_topic.domain.display_name | Physical Sciences |

| primary_topic.subfield.id | https://openalex.org/subfields/1703 |

| primary_topic.subfield.display_name | Computational Theory and Mathematics |

| primary_topic.display_name | Quantum-Dot Cellular Automata |

| cited_by_count | 0 |

| locations_count | 1 |

| best_oa_location.id | doi:10.5281/zenodo.17813133 |

| best_oa_location.is_oa | True |

| best_oa_location.source.id | https://openalex.org/S4306400562 |

| best_oa_location.source.issn | |

| best_oa_location.source.type | repository |

| best_oa_location.source.is_oa | True |

| best_oa_location.source.issn_l | |

| best_oa_location.source.is_core | False |

| best_oa_location.source.is_in_doaj | False |

| best_oa_location.source.display_name | Zenodo (CERN European Organization for Nuclear Research) |

| best_oa_location.source.host_organization | https://openalex.org/I67311998 |

| best_oa_location.source.host_organization_name | European Organization for Nuclear Research |

| best_oa_location.source.host_organization_lineage | https://openalex.org/I67311998 |

| best_oa_location.license | |

| best_oa_location.pdf_url | |

| best_oa_location.version | |

| best_oa_location.raw_type | article-journal |

| best_oa_location.license_id | |

| best_oa_location.is_accepted | False |

| best_oa_location.is_published | False |

| best_oa_location.raw_source_name | |

| best_oa_location.landing_page_url | https://doi.org/10.5281/zenodo.17813133 |

| primary_location.id | doi:10.5281/zenodo.17813133 |

| primary_location.is_oa | True |

| primary_location.source.id | https://openalex.org/S4306400562 |

| primary_location.source.issn | |

| primary_location.source.type | repository |

| primary_location.source.is_oa | True |

| primary_location.source.issn_l | |

| primary_location.source.is_core | False |

| primary_location.source.is_in_doaj | False |

| primary_location.source.display_name | Zenodo (CERN European Organization for Nuclear Research) |

| primary_location.source.host_organization | https://openalex.org/I67311998 |

| primary_location.source.host_organization_name | European Organization for Nuclear Research |

| primary_location.source.host_organization_lineage | https://openalex.org/I67311998 |

| primary_location.license | |

| primary_location.pdf_url | |

| primary_location.version | |

| primary_location.raw_type | article-journal |

| primary_location.license_id | |

| primary_location.is_accepted | False |

| primary_location.is_published | False |

| primary_location.raw_source_name | |

| primary_location.landing_page_url | https://doi.org/10.5281/zenodo.17813133 |

| publication_date | 2025-12-04 |

| publication_year | 2025 |

| referenced_works_count | 0 |

| abstract_inverted_index.a | 18, 59 |

| abstract_inverted_index.of | 49 |

| abstract_inverted_index.to | 57 |

| abstract_inverted_index.CPU | 27 |

| abstract_inverted_index.HDL | 21 |

| abstract_inverted_index.The | 11, 41 |

| abstract_inverted_index.and | 8, 34, 36, 64 |

| abstract_inverted_index.for | 24, 62 |

| abstract_inverted_index.its | 9 |

| abstract_inverted_index.the | 3, 14, 25, 47, 68 |

| abstract_inverted_index.two | 37 |

| abstract_inverted_index.(Pi, | 54 |

| abstract_inverted_index.Rate | 65 |

| abstract_inverted_index.This | 0 |

| abstract_inverted_index.core | 15 |

| abstract_inverted_index.face | 32 |

| abstract_inverted_index.main | 42 |

| abstract_inverted_index.Suite | 23 |

| abstract_inverted_index.token | 30 |

| abstract_inverted_index.Gamma, | 55 |

| abstract_inverted_index.Phi)** | 56 |

| abstract_inverted_index.Python | 39 |

| abstract_inverted_index.Senary | 5 |

| abstract_inverted_index.paper, | 17 |

| abstract_inverted_index.record | 1 |

| abstract_inverted_index.within | 67 |

| abstract_inverted_index.Verilog | 20 |

| abstract_inverted_index.**Cosmic | 52 |

| abstract_inverted_index.Electron | 6 |

| abstract_inverted_index.Paradigm | 7 |

| abstract_inverted_index.complete | 4 |

| abstract_inverted_index.distinct | 38 |

| abstract_inverted_index.includes | 13 |

| abstract_inverted_index.mapping, | 33 |

| abstract_inverted_index.presents | 2 |

| abstract_inverted_index.routing, | 31 |

| abstract_inverted_index.Constants | 53 |

| abstract_inverted_index.Control** | 66 |

| abstract_inverted_index.Sixtinary | 26 |

| abstract_inverted_index.establish | 58 |

| abstract_inverted_index.framework | 61 |

| abstract_inverted_index.(including | 28 |

| abstract_inverted_index.Blueprints | 22 |

| abstract_inverted_index.implements | 46 |

| abstract_inverted_index.irrational | 51 |

| abstract_inverted_index.simulator, | 43 |

| abstract_inverted_index.submission | 12 |

| abstract_inverted_index.**Coherence | 63 |

| abstract_inverted_index.Simulators. | 40 |

| abstract_inverted_index.arithmetic, | 29 |

| abstract_inverted_index.fundamental | 50 |

| abstract_inverted_index.integration | 48 |

| abstract_inverted_index.theoretical | 16, 60 |

| abstract_inverted_index.pigamafi.py, | 45 |

| abstract_inverted_index.sixtaidryson | 44 |

| abstract_inverted_index.architecture. | 69 |

| abstract_inverted_index.comprehensive | 19 |

| abstract_inverted_index.testbenches), | 35 |

| abstract_inverted_index.implementation. | 10 |

| cited_by_percentile_year | |

| countries_distinct_count | 0 |

| institutions_distinct_count | 1 |

| citation_normalized_percentile.value | 0.8213335 |

| citation_normalized_percentile.is_in_top_1_percent | False |

| citation_normalized_percentile.is_in_top_10_percent | False |