Design Hybrid Architecture to Implement AES Algorithm on FPGA for IoT Applications Article Swipe

YOU?

·

· 2024

· Open Access

·

· DOI: https://doi.org/10.21123/bsj.2024.8931

YOU?

·

· 2024

· Open Access

·

· DOI: https://doi.org/10.21123/bsj.2024.8931

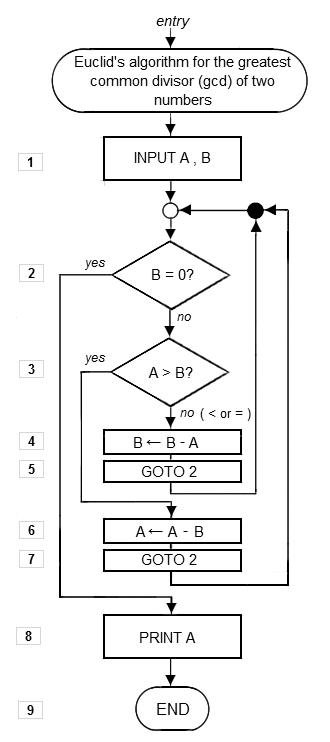

تتطلب خوارزميات التشفير عالية الأمان مثل AES قدرات حسابية عالية لتحقيق أمن المعلومات. لذلك، من الضروري استخدام بنيات الحوسبة المتوازية التي تستغل التقنيات الحديثة في التوازيات المكانية للحصول على أكبر قدر من القوة الحسابية التي يمكن تصورها. تم إدخال تقنيات مختلفة لتحقيق المعالجة المتوازية. إحداها هي مصفوفات البوابات القابلة للبرمجة ميدانيًا (FPGAs)، والتي تتميز بخصائص جيدة مناسبة لتنفيذ بنيات متوازية مع استهلاك أقل للطاقة. تهدف الورقة إلى تصميم وتنفيذ جهاز إرسال واستقبال مدمج لبنية محرك المعالجة الحاسوبية ذو أداء عالٍ للحصول على إنتاجية أفضل على تقنية FPGA لتشفير وفك تشفير الصور. في هذا التصميم، تم استخدام لوحتين، "DE1_Soc و NEEK board" مع جهاز Altera Quartus prime 18.1، وجهاز cyclone V 5CSEMA5F31C6 FPGA للتوليف والمحاكاة. أظهرت نتائج التنفيذ أن البنية المقترحة تتمتع بكفاءة الأداء من حيث تردد التشغيل 600 ميكا هرتز والإنتاجية 76.8 كيكا هرتز.

Related Topics To Compare & Contrast

- Type

- article

- Language

- ar

- Landing Page

- https://doi.org/10.21123/bsj.2024.8931

- OA Status

- gold

- Cited By

- 2

- References

- 34

- Related Works

- 10

- OpenAlex ID

- https://openalex.org/W4404520422