Phased-Array Antenna Beam Control System Design Based on HLS Plus RTL Mode Article Swipe

YOU?

·

· 2025

· Open Access

·

· DOI: https://doi.org/10.9790/0853-2003021521

YOU?

·

· 2025

· Open Access

·

· DOI: https://doi.org/10.9790/0853-2003021521

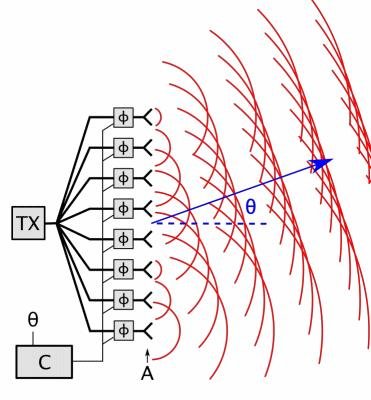

Background: In recent years, the rising demand for high-performance radar systems in aeronautics, astronautics, national defense, and civil communication has driven the widespread application of phased-array technology. The design of beam controllers, the core of phased-array systems, faces many challenges. Traditional implementation schemes are usually based on application-specific integrated circuits (ASIC) or discrete components, which have a long development cycle, poor flexibility, and limited adaptability. Field-programmable gate arrays (FPGA), with their high parallelism, reconfigurability, and powerful signal processing capabilities, offer a new way to implement phased-array control systems. But FPGA design has traditionally relied on register transfer level (RTL) description, which is inefficient and struggles to keep up with the rapid iteration of complex algorithms. With the development of high-level synthesis (HLS) technology, it has become possible to develop FPGAs using high-level languages such as C/C++. However, improving development efficiency while ensuring hardware performance remains a key issue in the design of phased-array beam controllers. Materials and Methods: This study employs an HLS - RTL co - design method to build a phased - array beam controller. This approach combines the strengths of HLS's efficient algorithm implementation and RTL's precise hardware interface control. The system architecture consists of three parts: the host - machine control layer, FPGA processing layer, and phase - control output layer. In the FPGA processing layer, the core beam - forming algorithm is implemented via HLS. Based on phased - array principles, this algorithm converts target angles to wave vectors and calculates phase - compensation values for each element in an 8×8 array. Pipelining and parallel processing techniques are used in the HLS design to optimize algorithm throughput and latency. The phase - control output layer, designed with RTL, repackages 64 calculated phase values and distributes them to 16 physical phase - shifter chips. Each phase - shifter manages four elements and receives control data through an SPI interface. Results: The proposed FPGA-based phased-array beam controller design in this paper has successfully achieved high - speed, high - precision beam control. By using the HLS - RTL co - design method, it has solved the problem of low algorithm implementation efficiency in traditional FPGA development and ensured the high performance and reliability of hardware interfaces. Experimental results indicate that the system meets or surpasses design targets on key performance indicators. Its end - to - end latency is kept within 130μs, it supports an angle update rate of over 5,000 times per second, and can satisfy the requirements for tracking highly dynamic targets in practical applications. Conclusion: The major contributions of this research are as follows: presenting an HLS - RTL co - design methodology for complex FPGA system development; designing an efficient phased - array beam - forming algorithm and its hardware implementation; and developing a flexible and scalable phased - array control system architecture that supports different array configurations. These findings are highly significant for beamforming technologies in phased - array radar and 5G communication systems, as well as for other FPGA applications requiring high - speed signal processing.

Related Topics To Compare & Contrast

- Type

- article

- Language

- en

- Landing Page

- https://doi.org/10.9790/0853-2003021521

- https://doi.org/10.9790/0853-2003021521

- OA Status

- bronze

- References

- 8

- Related Works

- 10

- OpenAlex ID

- https://openalex.org/W4411706551